Altera Corporation 5–38

July 2005 Stratix Device Handbook, Volume 2

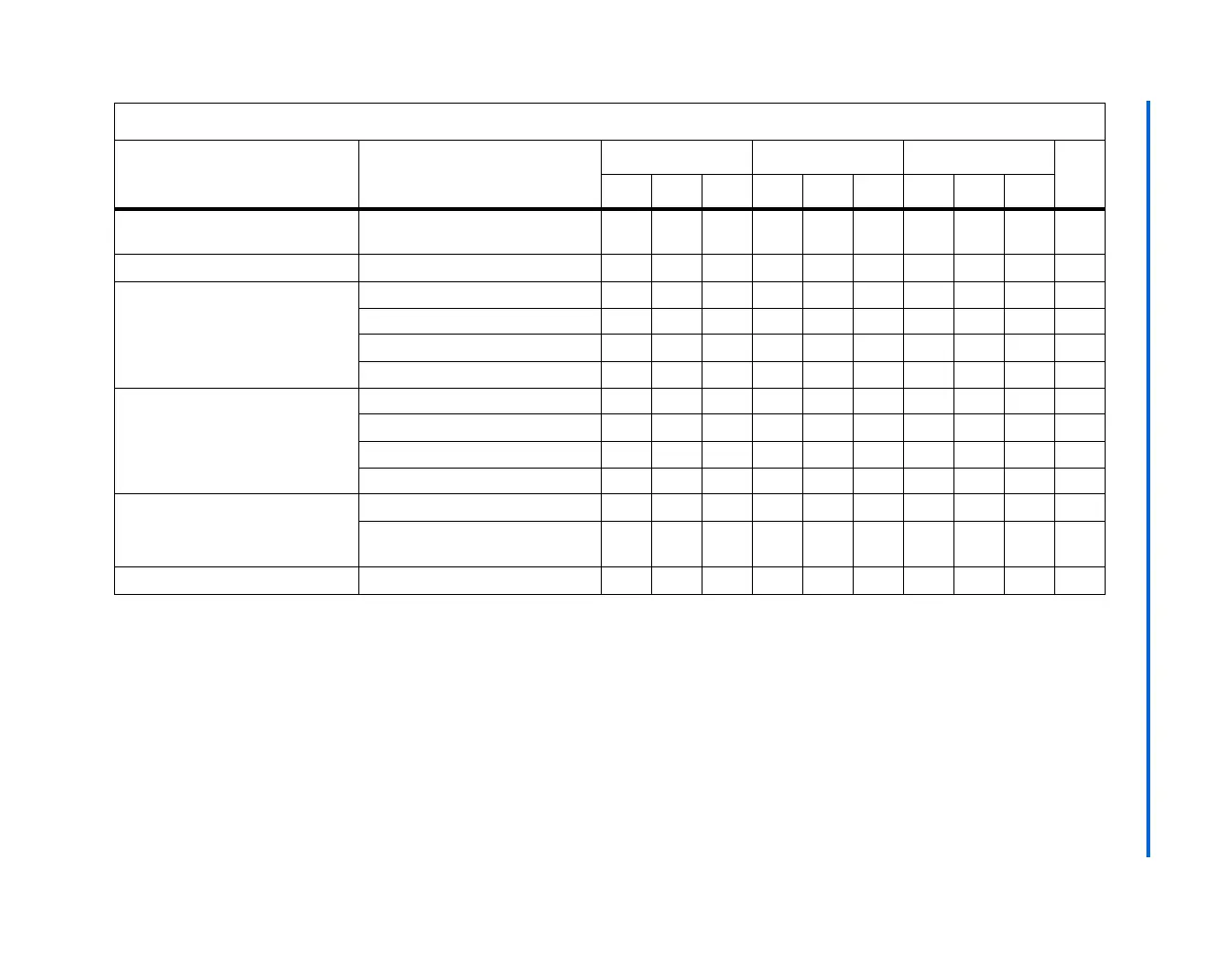

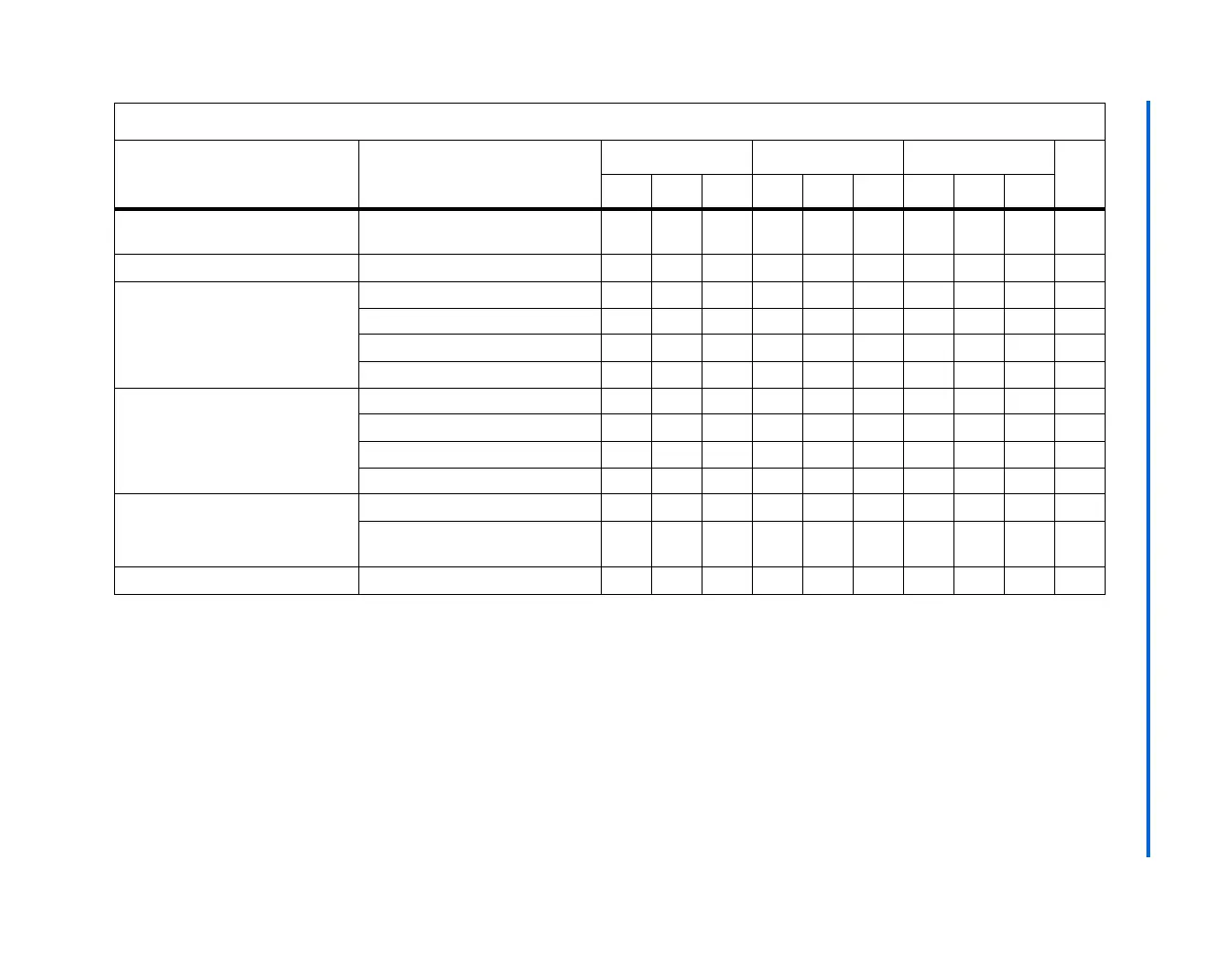

Source-Synchronous Timing Budget

Input jitter tolerance (peak-to-

peak)

All 250 250 250 ps

Output jitter (peak-to-peak) All 200 200 200 ps

Output t

RISE

LVDS 80 110 120 80 110 120 80 110 120 ps

HyperTransport technology 120 170 200 120 170 200 120 170 200 ps

LVPECL 100 135 150 100 135 150 100 135 150 ps

PCML 80 110 135 80 110 135 80 110 135 ps

Output t

FALL

LVDS 80 110 120 80 110 120 80 110 120 ps

HyperTransport 110 170 200 110 170 200 110 170 200 ps

LVPECL 100 135 160 100 135 160 100 135 160 ps

PCML 110 145 175 110 145 175 110 145 175 ps

t

DUTY

LVDS (J =2..10) only 47.5 50 52.5 47.5 50 52.5 47.5 50 52.5 %

LVDS (J =1) and LVPECL, PCML,

HyperTransport technology

45 50 55 45 50 55 45 50 55 %

t

LOCK

All 100 100 100 μs

Table 5–8. High-Speed I/O Specifications for Wire-Bond Packages (Part 3 of 3)

Symbol Conditions

-6 Speed Grade -7 Speed Grade -8 Speed Grade

Unit

Min Typ Max Min Typ Max Min Typ Max

Loading...

Loading...