Altera Corporation 5–37

July 2005 Stratix Device Handbook, Volume 2

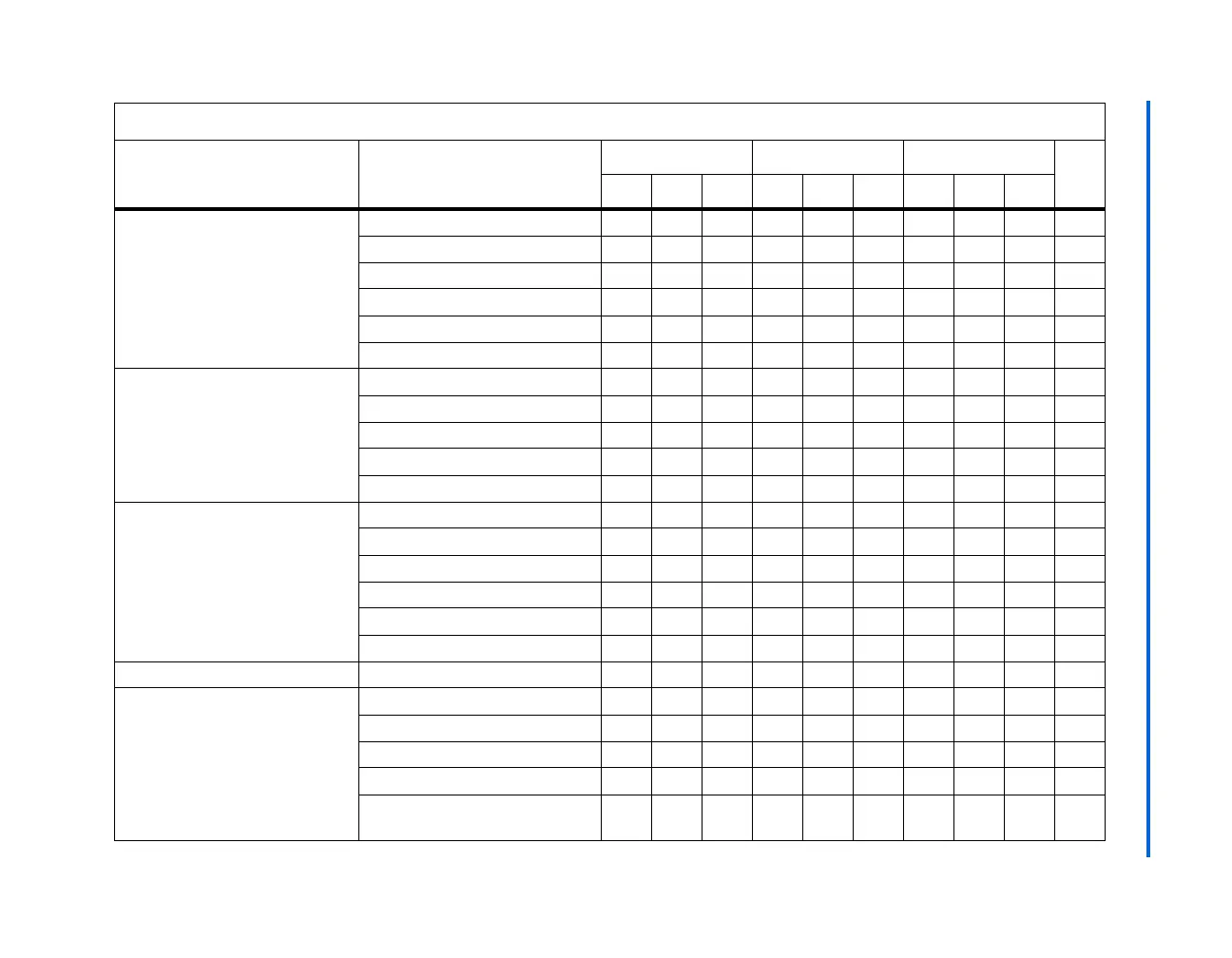

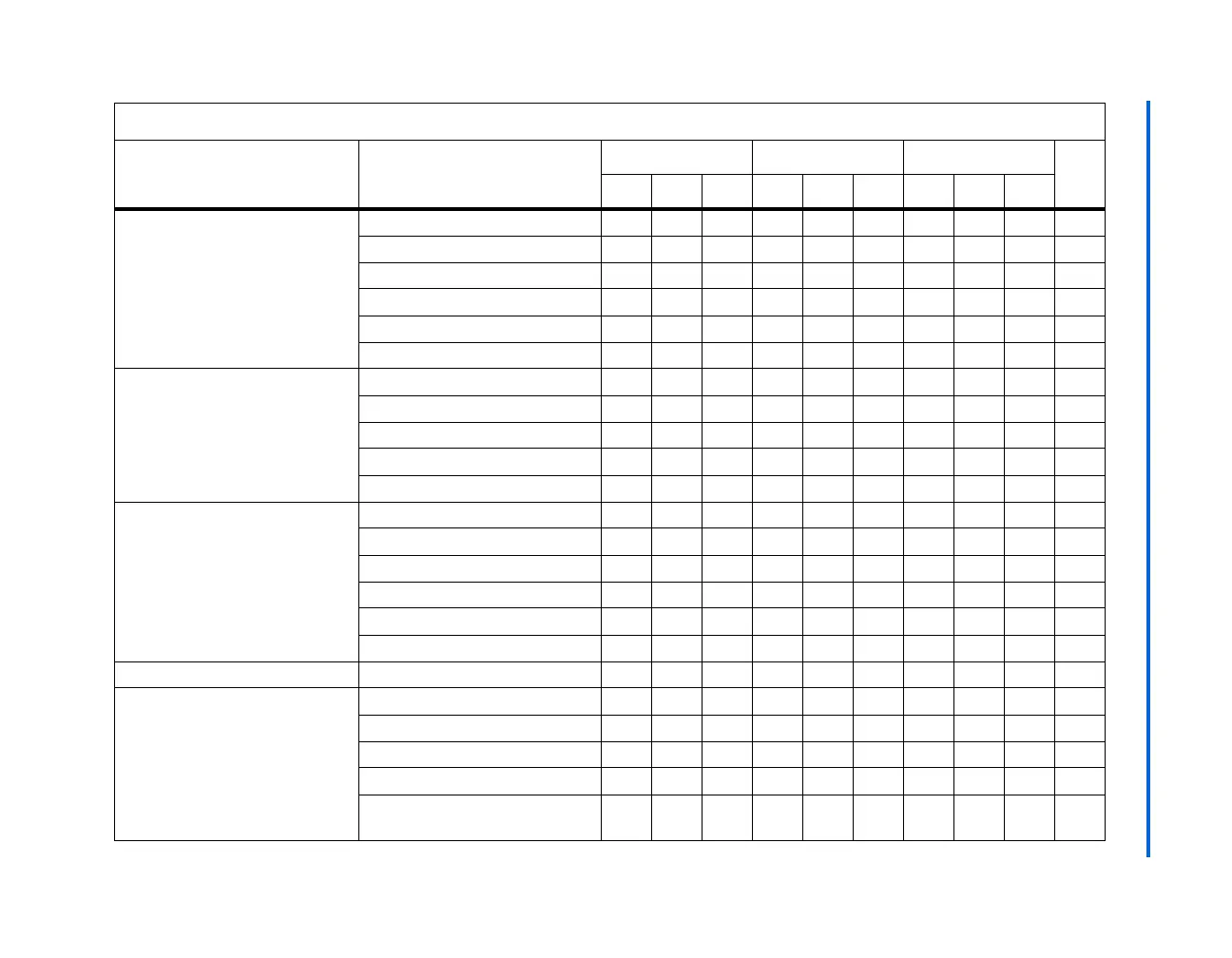

Source-Synchronous Timing Budget

f

HSDR

Device operation,

(LVDS,LVPECL, HyperTransport

technology)

J = 10 300 624 300 462 300 462 Mbps

J = 8 300 624 300 462 300 462 Mbps

J = 7 300 624 300 462 300 462 Mbps

J = 4 300 624 300 462 300 462 Mbps

J = 2 100 462 100 462 100 462 Mbps

J = 1 (LVDS and LVPECL only) 100 311 100 270 100 270 Mbps

f

HSCLK

(Clock frequency)

(PCML)

f

HSCLK

= f

HSDR

/ W

W = 4 to 30 (Serdes used) 10 77.75 MHz

W = 2 (Serdes bypass) 50 150 50 77.5 50 77.5 MHz

W = 2 (Serdes used) 150 155.5 MHz

W = 1 (Serdes bypass) 100 200 100 155 100 155 MHz

W = 1 (Serdes used) 300 311 MHz

Device operation, f

HSDR

(PCML)

J = 10 300 311 Mbps

J = 8 300 311 Mbps

J = 7 300 311 Mbps

J = 4 300 311 Mbps

J = 2 100 300 100 155 100 155 Mbps

J = 1 100 200 100 155 100 155 Mbps

TCCS All 400 400 400 ps

SW PCML (J = 4, 7, 8, 10) only 800 800 800 ps

PCML (J = 2) only 1,200 1,200 1,200 ps

PCML (J = 1) only 1,700 1,700 1,700 ps

LVDS and LVPECL (J = 1) only 550 550 550 ps

LVDS, LVPECL, HyperTransport

technology (J = 2 through 10) only

500 500 500 ps

Table 5–8. High-Speed I/O Specifications for Wire-Bond Packages (Part 2 of 3)

Symbol Conditions

-6 Speed Grade -7 Speed Grade -8 Speed Grade

Unit

Min Typ Max Min Typ Max Min Typ Max

Loading...

Loading...