5–36 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

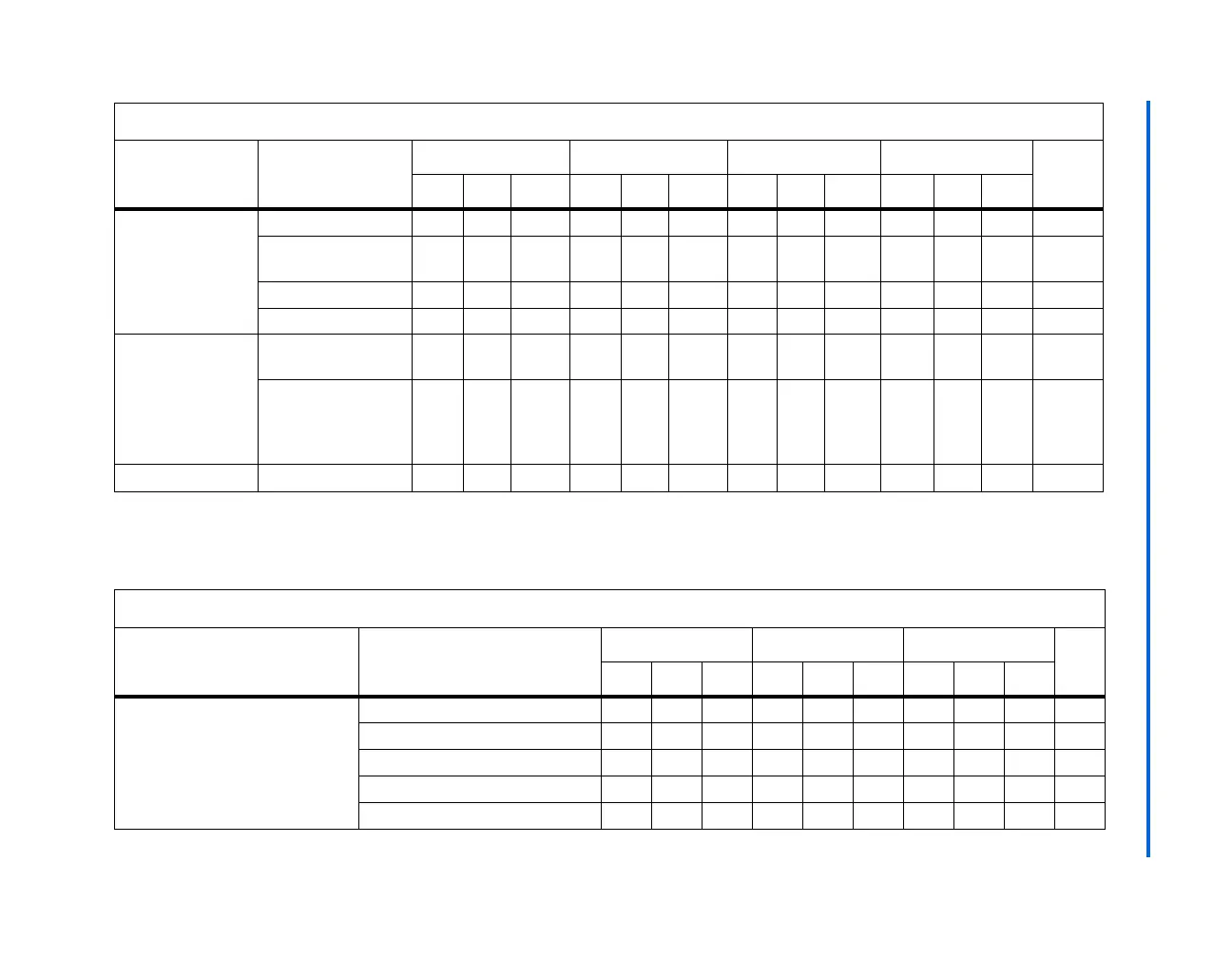

Source-Synchronous Timing Budget

Output t

FALL

LVDS 80 110 120 80 110 120 80 110 120 80 110 120 ps

HyperTransport

technology

110 170 200 110 170 200 110 170 200 110 170 200 ps

LVPECL 90 130 160 90 130 160 100 135 160 100 135 160 ps

PCML 105 140 175 105 140 175 110 145 175 110 145 175 ps

t

DUTY

LVDS (J = 2 through

10)

47.5 50 52.5 47.5 50 52.5 47.5 50 52.5 47.5 50 52.5 %

LVDS (J =1) and

LVPECL, PCML,

HyperTransport

technology

45 50 55 45 50 55 45 50 55 45 50 55 %

t

LOCK

All 100 100 100 100 μs

Notes to Ta b le 5 – 7 :

(1) When J = 4, 7, 8, and 10, the SERDES block is used.

(2) When J = 2 or J = 1, the SERDES is bypassed.

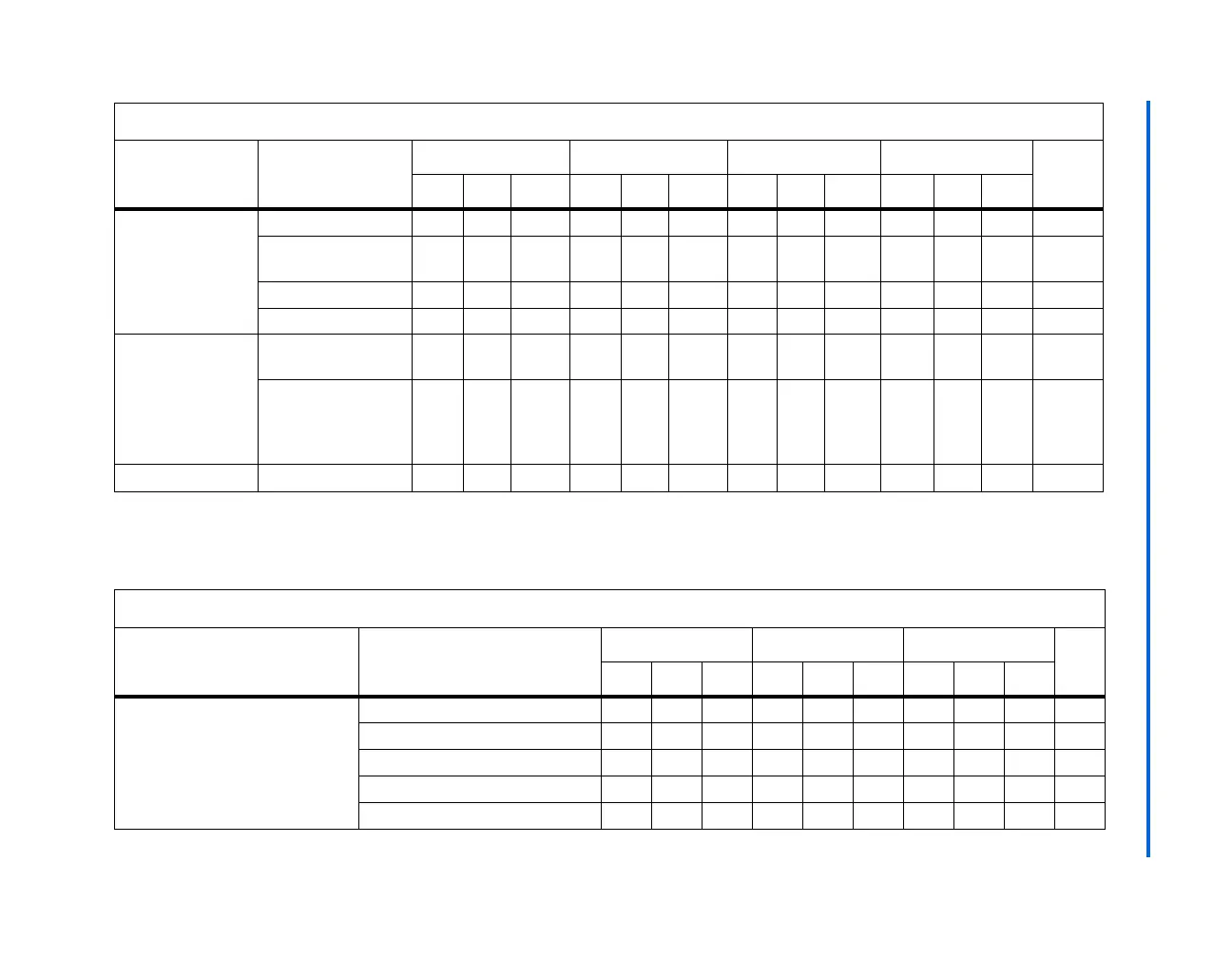

Table 5–8. High-Speed I/O Specifications for Wire-Bond Packages (Part 1 of 3)

Symbol Conditions

-6 Speed Grade -7 Speed Grade -8 Speed Grade

Unit

Min Typ Max Min Typ Max Min Typ Max

f

HSCLK

(Clock frequency)

(LVDS,LVPECL, HyperTransport

technology)

f

HSCLK

= f

HSDR

/ W

W = 4 to 30 (Serdes used) 10 156 10 115.5 10 115.5 MHz

W = 2 (Serdes bypass) 50 231 50 231 50 231 MHz

W = 2 (Serdes used) 150 312 150 231 150 231 MHz

W = 1 (Serdes bypass) 100 311 100 270 100 270 MHz

W = 1 (Serdes used) 300 624 300 462 300 462 MHz

Table 5–7. High-Speed I/O Specifications for Flip-Chip Packages (Part 3 of 3) Notes (1), (2)

Symbol Conditions

-5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade

Unit

Min Typ Max Min Typ Max Min Typ Max Min Typ Max

Loading...

Loading...