Altera Corporation 5–69

July 2005 Stratix Device Handbook, Volume 2

High-Speed Differential I/O Interfaces in Stratix Devices

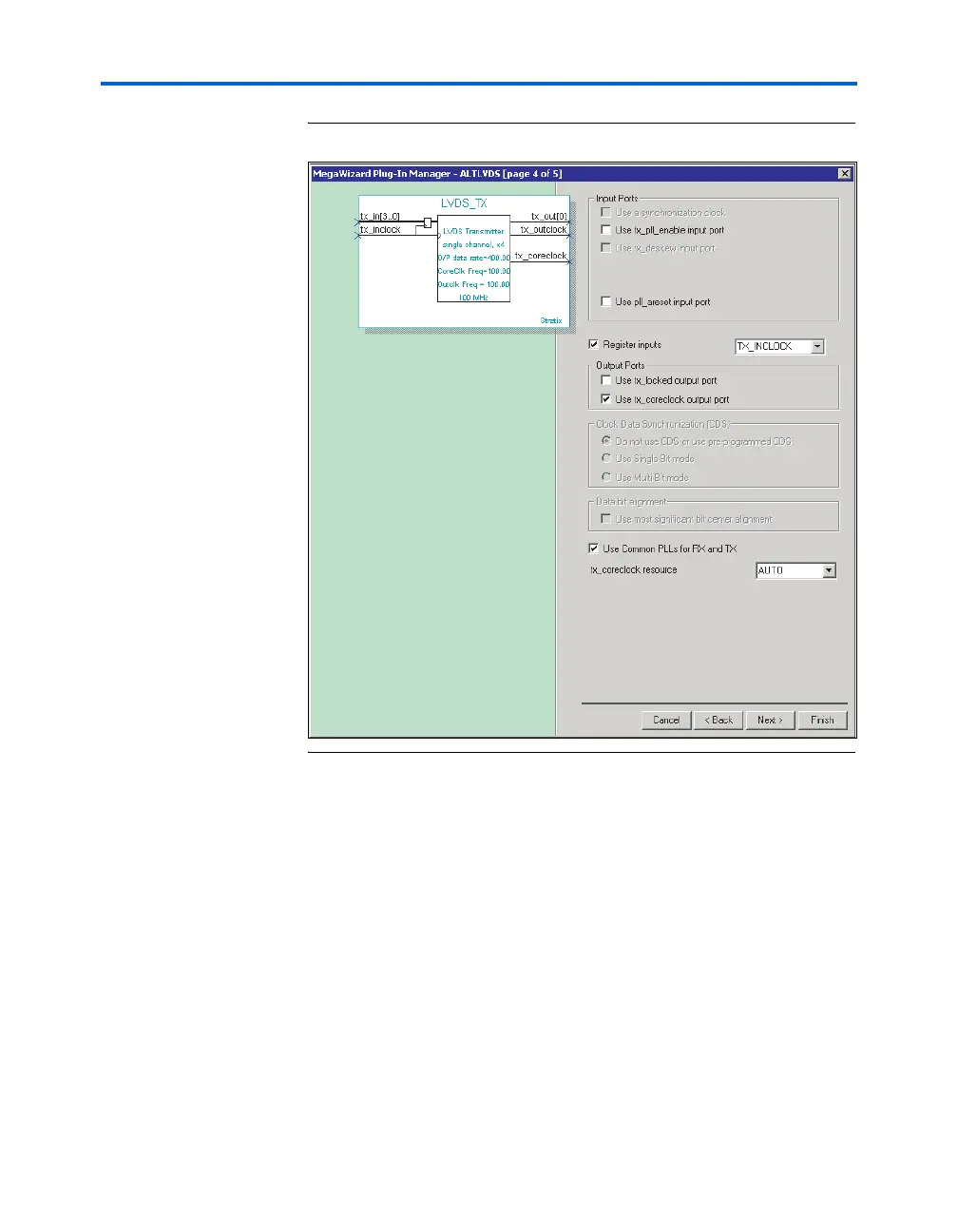

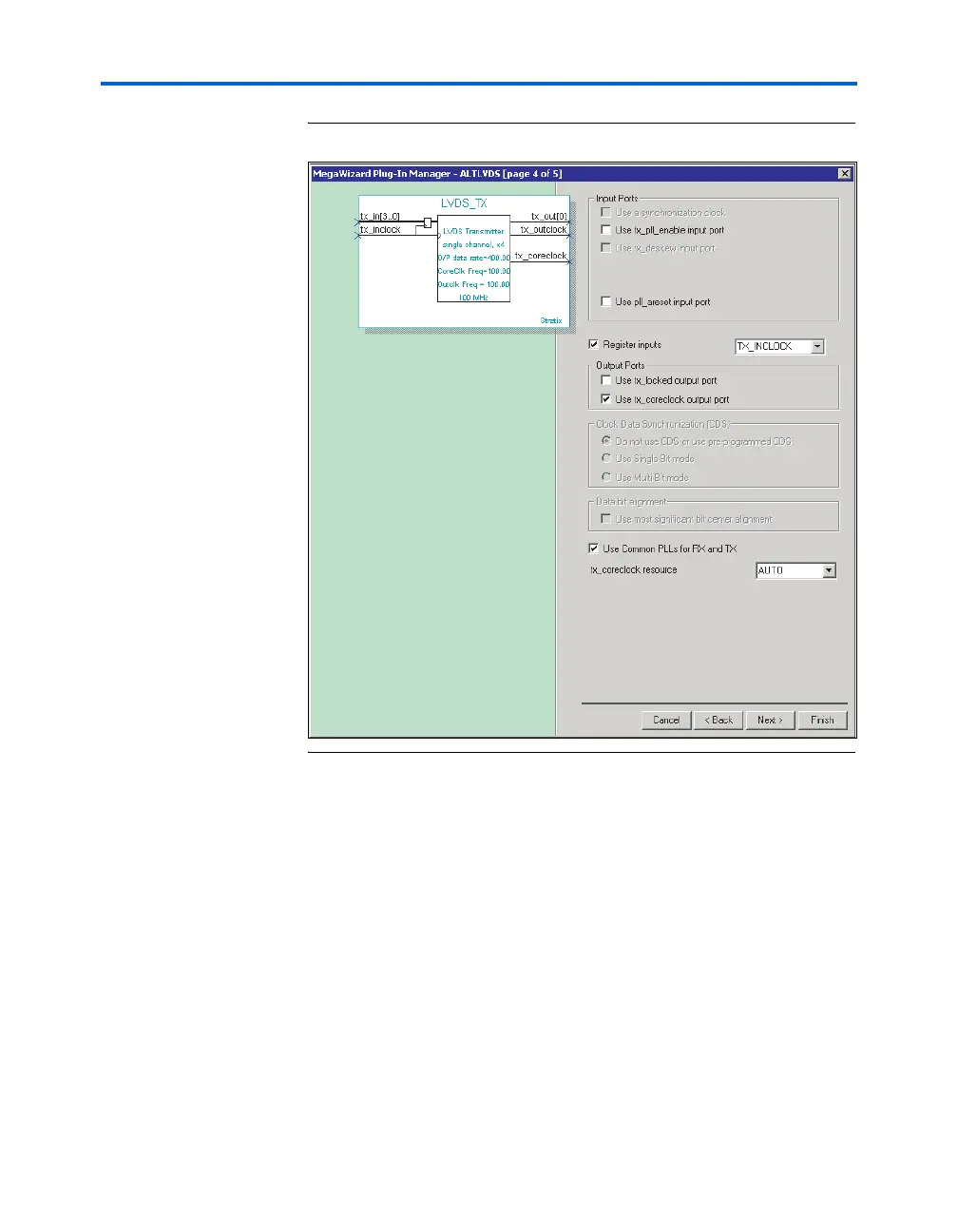

Figure 5–43. Page 4 of the Transmitter altlvds MegaWizard Plug-In Manager

Registered Inputs

Check the Register inputs box if the input data to the transmitter is not

registered just before it feeds the transmitter module. You can choose

either tx_clkin or tx_coreclk to clock the transmitter data

(tx_in[]) signal. This serves as the register boundary. The number of

registers used is proportional to the deserialization factor (J). The

Quartus II software places the synchronization registers with the LEs in

the same row and closest to the SERDES circuitry.

Use Common PLL for Transmitter & Receiver

Check the Use Common PLLs for Rx and Tx box to place both the LVDS

transmitter and receiver in the same I/O bank in Stratix devices. The

Quartus II software also allows the transmitter and receiver to share the

PLL when the same input clock is used for both. Although you must

Loading...

Loading...