Altera Corporation 1–19

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

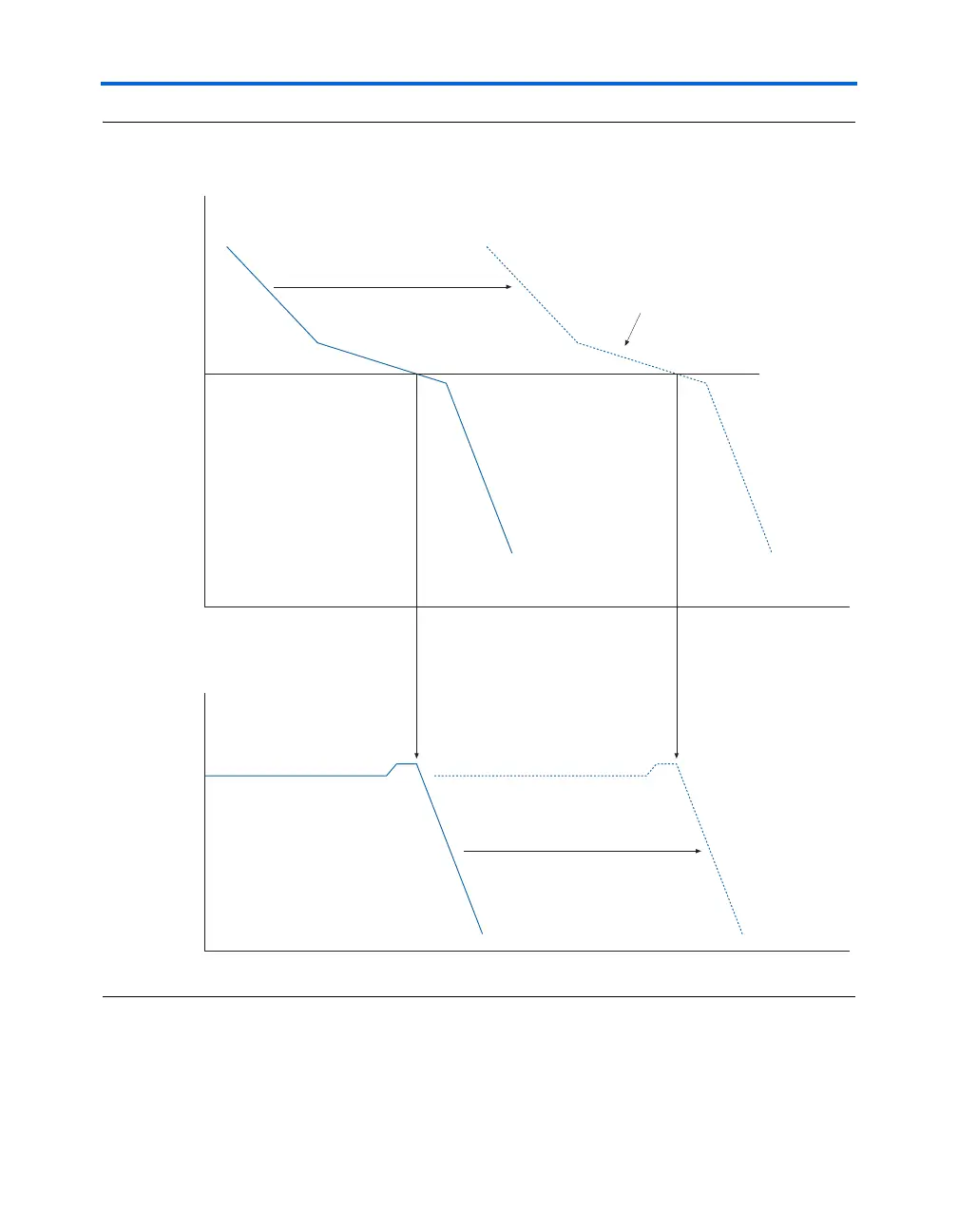

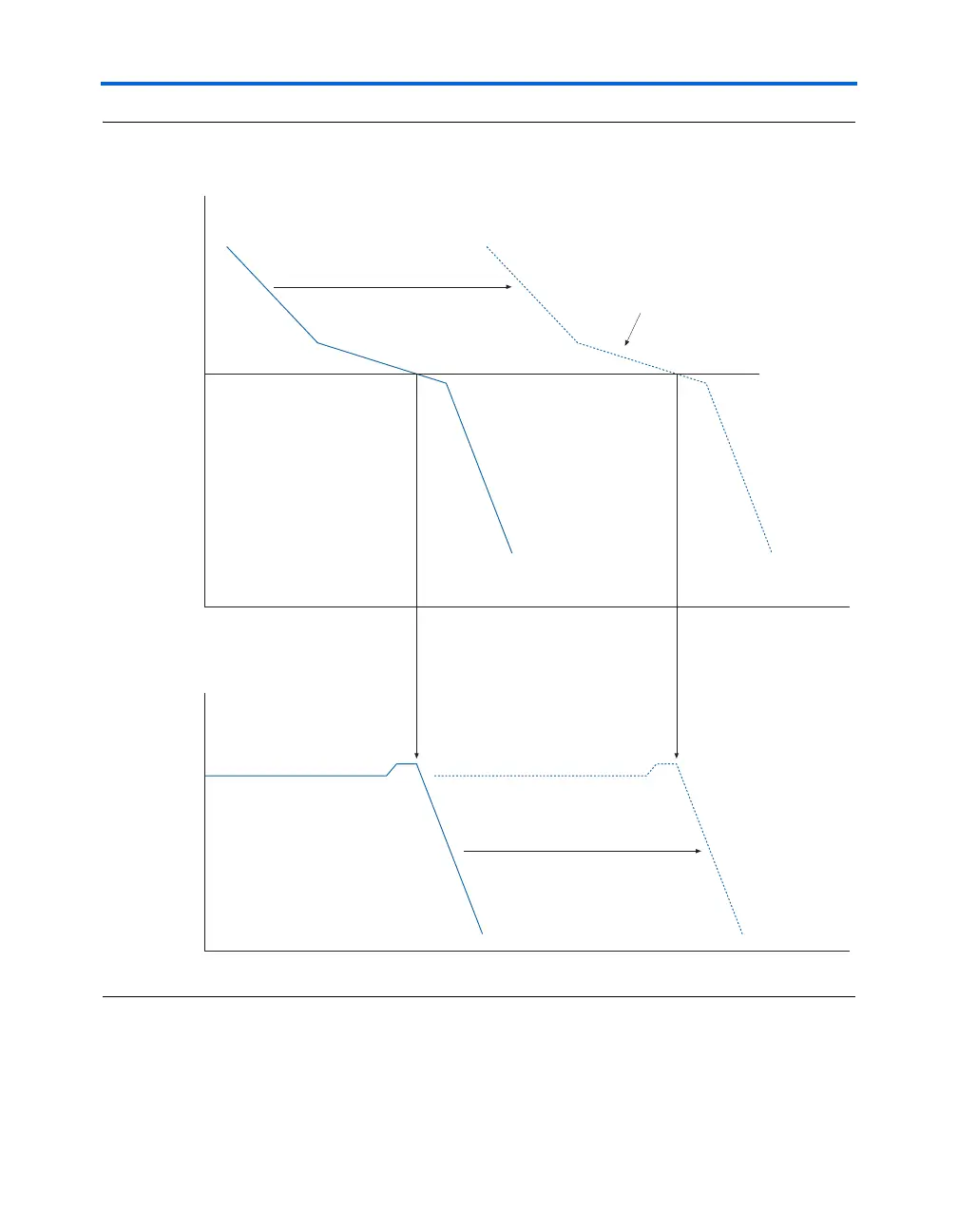

Figure 1–8. Open- & Closed-Loop Response Bode Plots

A high-bandwidth PLL provides a fast lock time and tracks jitter on the

reference clock source, passing it through to the PLL output. A low-

bandwidth PLL filters out reference clock jitter, but increases lock time.

Stratix device enhanced PLLs allow you to control the bandwidth over a

Increasing the PLL's

bandwidth in effect pushes

the open loop response out.

Gain

Gain

0 dB

Frequency

Frequency

Open-Loop Reponse Bode Plot

Closed-Loop Reponse Bode Plot

Loading...

Loading...