1–20 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Enhanced PLLs

finite range to customize the PLL characteristics for a particular

application. Applications that require clock switchover (such as TDMA,

frequency hopping wireless, and redundant clocking) can benefit from

the programmable bandwidth feature of the Stratix and Stratix GX PLLs.

The bandwidth and stability of such a system is determined by a number

of factors including the charge pump current, the loop filter resistor

value, the high-frequency capacitor value (in the loop filter), and the m-

counter value. You can use the Quartus II software to control these factors

and to set the bandwidth to the desired value within a given range.

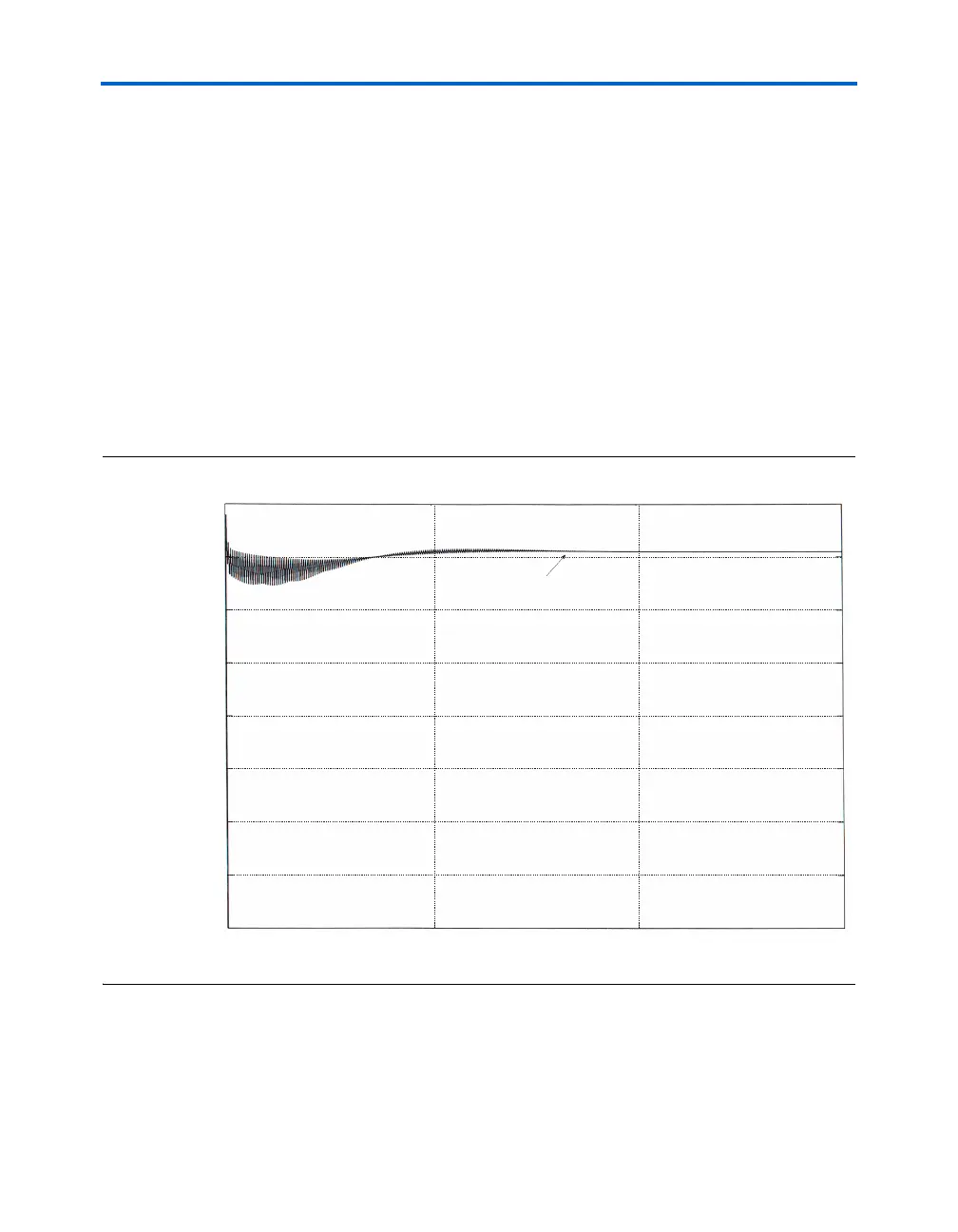

You can set the bandwidth to the appropriate value to balance the need

for jitter filtering and lock time. Figures 1–9 and 1–10 show the output of

a low- and high-bandwidth PLL, respectively, as it locks onto the input

clock.

Figure 1–9. Low-Bandwidth PLL Lock Time

05 1510

Time (μs)

Frequency (MHz)

120

125

130

135

140

145

150

155

160

Lock Time = 8 μs

Loading...

Loading...