Altera Corporation 1–21

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

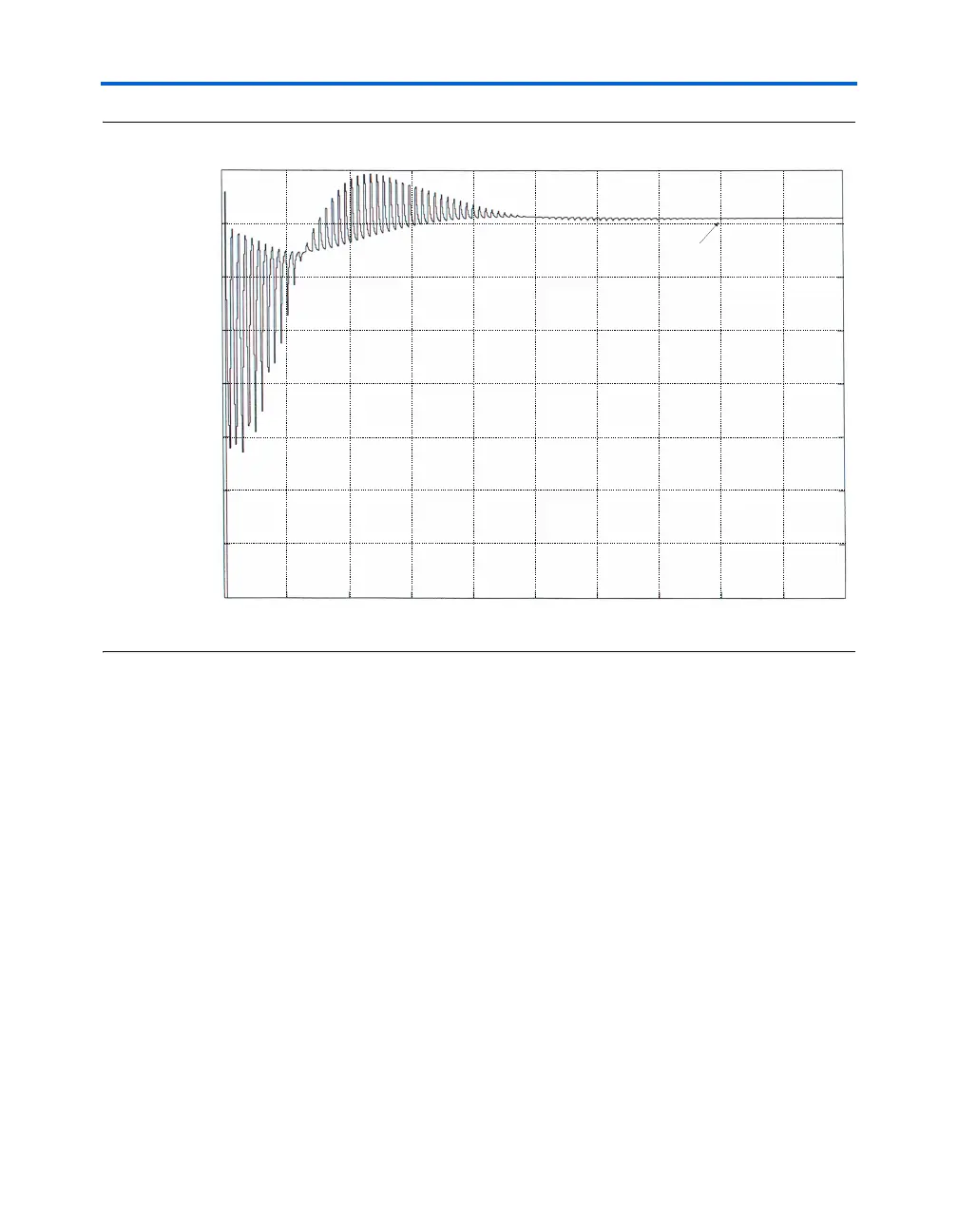

Figure 1–10. High-Bandwidth PLL Lock Time

A high-bandwidth PLL may benefit a system with two cascaded PLLs. If

the first PLL uses spread spectrum (as user-induced jitter), the second

PLL needs a high bandwidth so it can track the jitter that is feeding it. A

low-bandwidth PLL may, in this case, lose lock due to the spread

spectrum-induced jitter on the input clock.

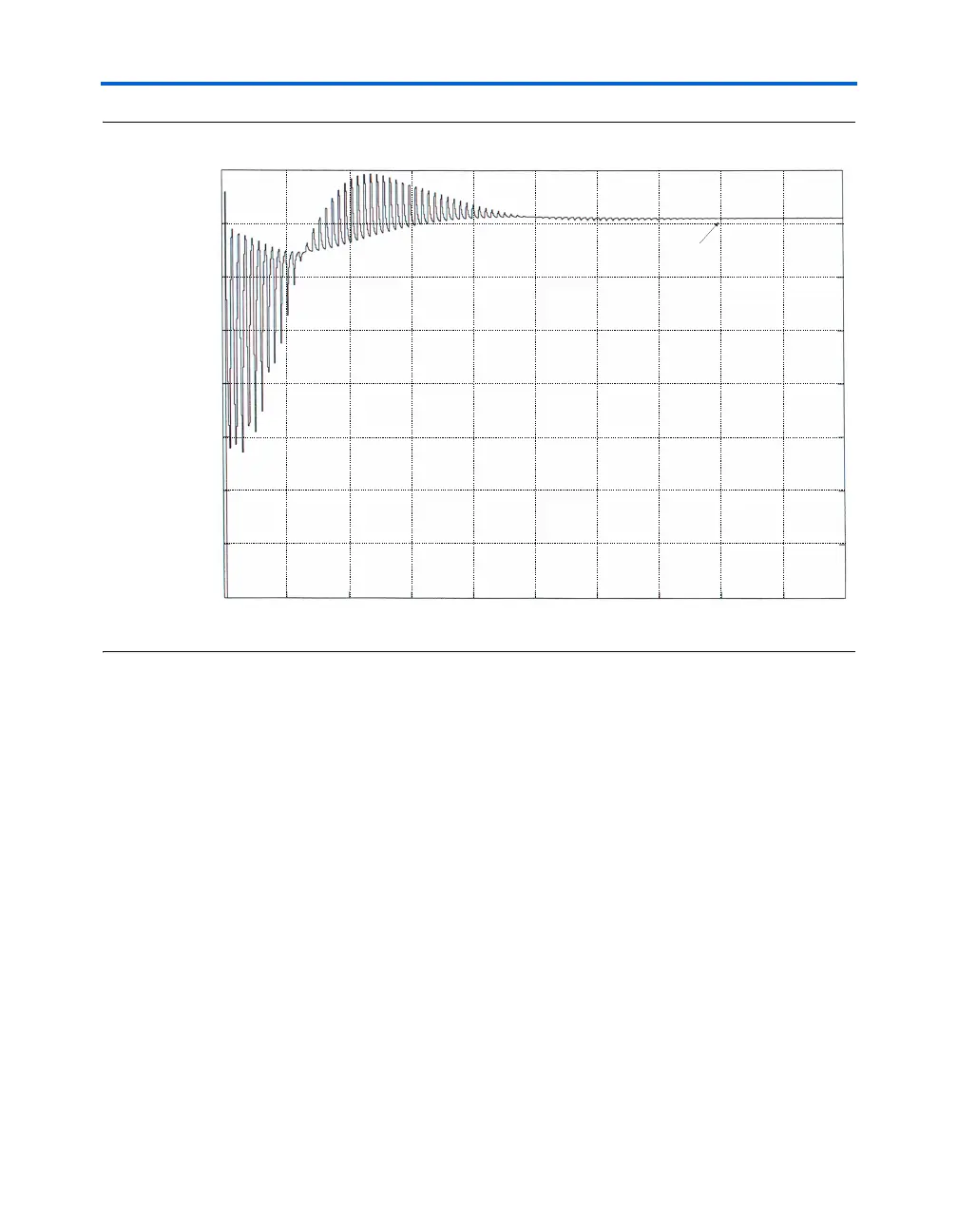

A low-bandwidth PLL may benefit a system using clock switchover.

When the clock switchover happens, the PLL input temporarily stops. A

low-bandwidth PLL would react more slowly to changes to its input

clock and take longer to drift to a lower frequency (caused by the input

stopping) than a high-bandwidth PLL. Figures 1–11 and 1–12

demonstrate this property.

The two plots show the effects of clock switchover with a low- or high-

bandwidth PLL. When the clock switchover happens, the output of the

low-bandwidth PLL (see Figure 1–11) drifts to lower frequency much

slower than the high-bandwidth PLL output (see Figures 1–12).

0

120

125

130

135

140

145

150

155

160

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

Time (μs)

Frequency (MHz)

Lock Time = 4 μs

Loading...

Loading...