Altera Corporation 1–23

July 2005 Stratix Device Handbook, Volume 2

General-Purpose PLLs in Stratix & Stratix GX Devices

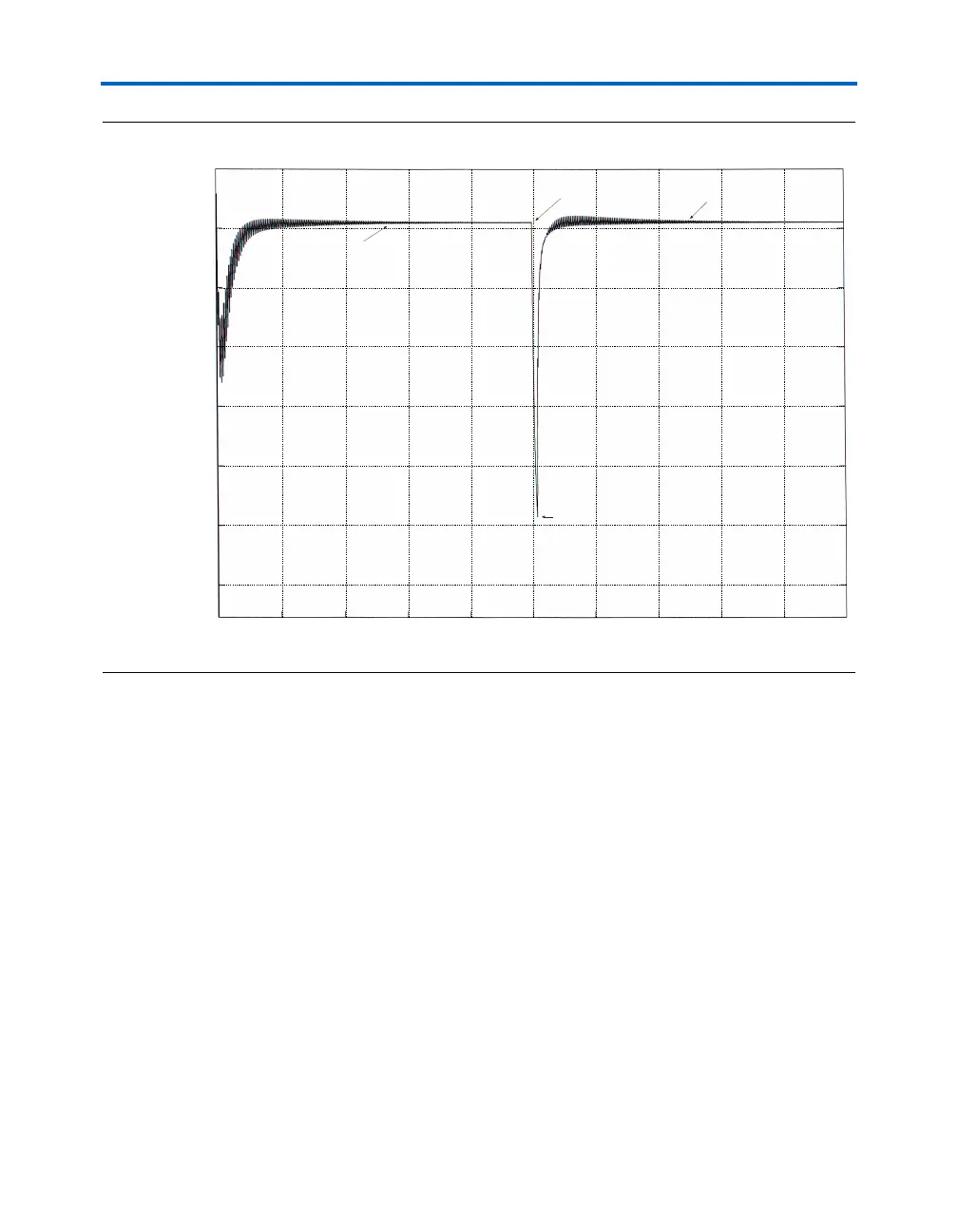

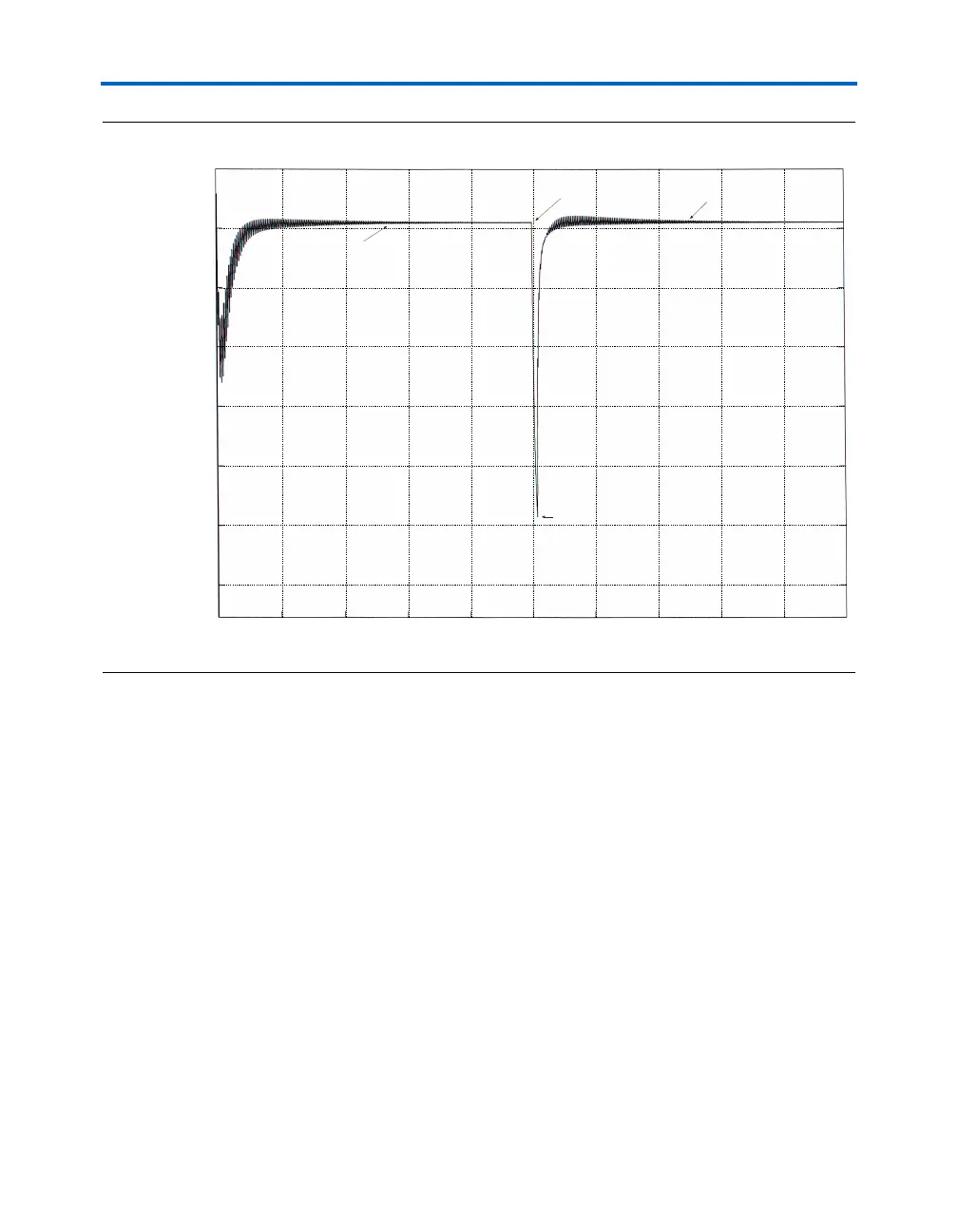

Figure 1–12. Effect of High Bandwidth on Clock Switchover

Implementation

Traditionally, external components such as the VCO or loop filter control

a PLL’s bandwidth. Most loop filters are made up of passive components,

such as resistors and capacitors, which take up unnecessary board space

and increase cost. With Stratix and Stratix GX device enhanced PLLs, all

the components are contained within the device to increase performance

and decrease cost.

Stratix and Stratix GX device enhanced PLLs implement programmable

bandwidth by giving you control of the charge pump current and loop

filter resistor (R) and high-frequency capacitor (C

h

) values (see

Table 1–8). The Stratix and Stratix GX device enhanced PLL bandwidth

ranges from approximately 150 kHz to 2 MHz.

0

125

130

135

140

145

150

155

160

2 4 6 8 10 12 14 16 18 20

Time (μs)

Frequency (MHz)

Initial Lock

Input Clock Stops

Re-lock

Switchover

Loading...

Loading...