8–20 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Interfaces

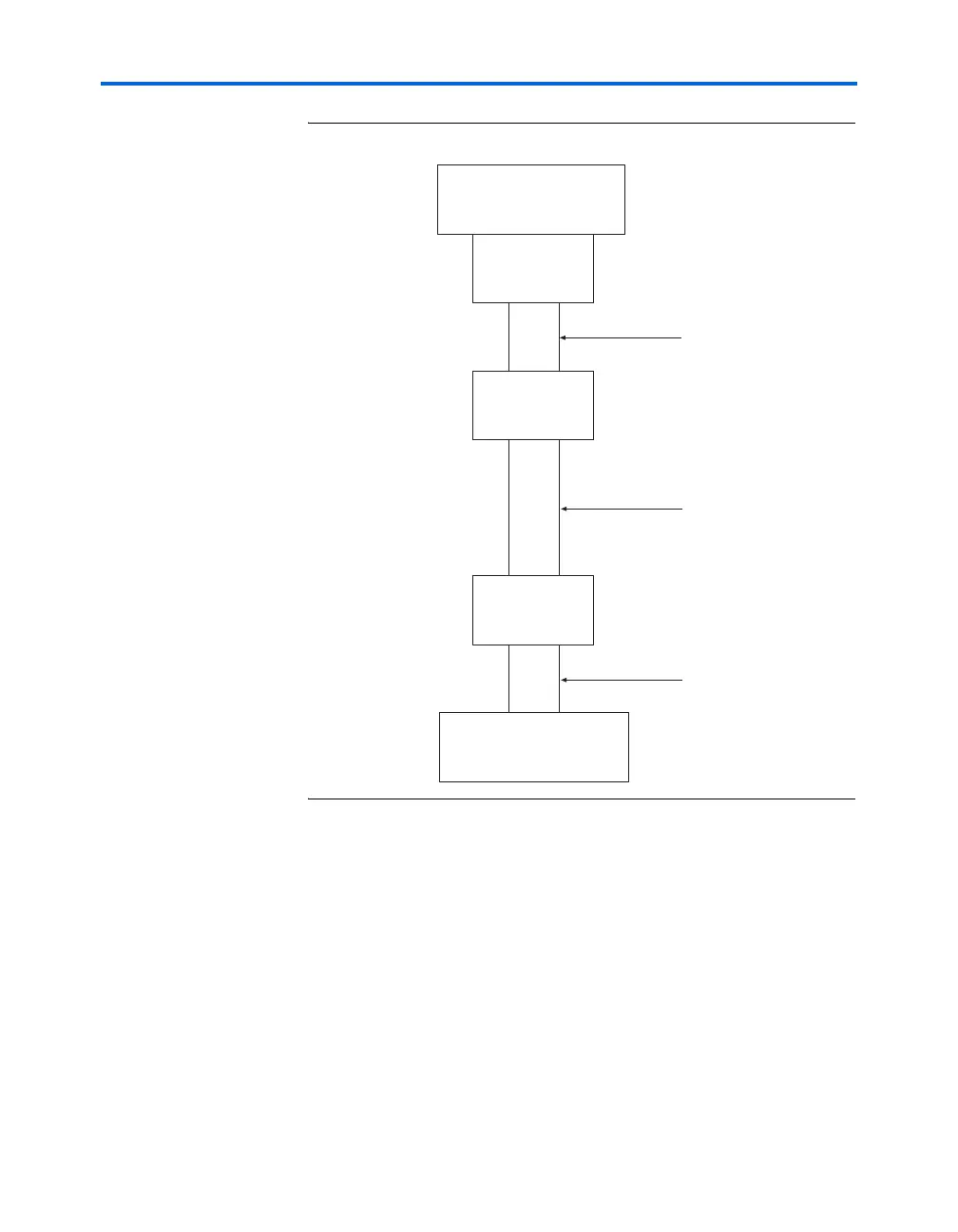

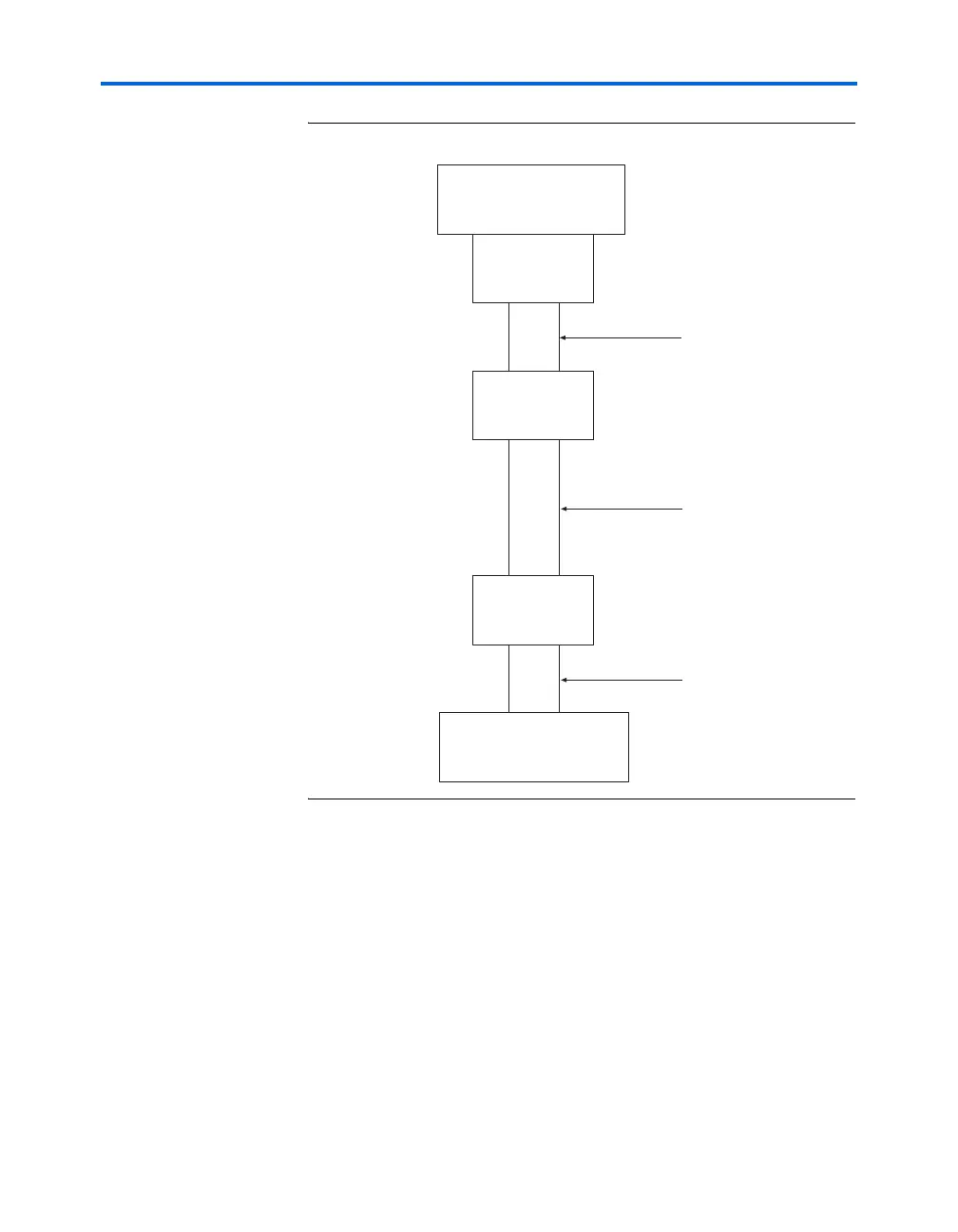

Figure 8–15. XAUI Location

Functional Description

XAUI can replace the 32 bits of parallel data required by XGMII for

transmission with just 4 lanes of serial data. XAUI uses clock data

recovery (CDR) to eliminate the need for separate clock signals. 8b/10b

encoding is employed on the data stream to embed the clock in the data.

The 8b/10b protocol to encode an 8-bit word stream to 10-bit codes that

results in a DC-balanced serial stream and eases the receiver

synchronization. To support 10-Gigabit Ethernet, each lane must run at a

speed of at least 2.5 Gbps. Using 8b/10b encoding increases the rate for

each lane to 3.125 Gbps, which will be supported in Stratix GX Gbps

devices. This circuitry is supported by the embedded 3.125 Gbps

transceivers within the Stratix GX architecture. You can find more

XGXS

PHY

XAUI

XGMII

XGMII

Reconciliation

MAC

XGMII Extender

Sublayer (XGXS)

Loading...

Loading...