Altera Corporation 8–21

July 2005 Stratix Device Handbook, Volume 2

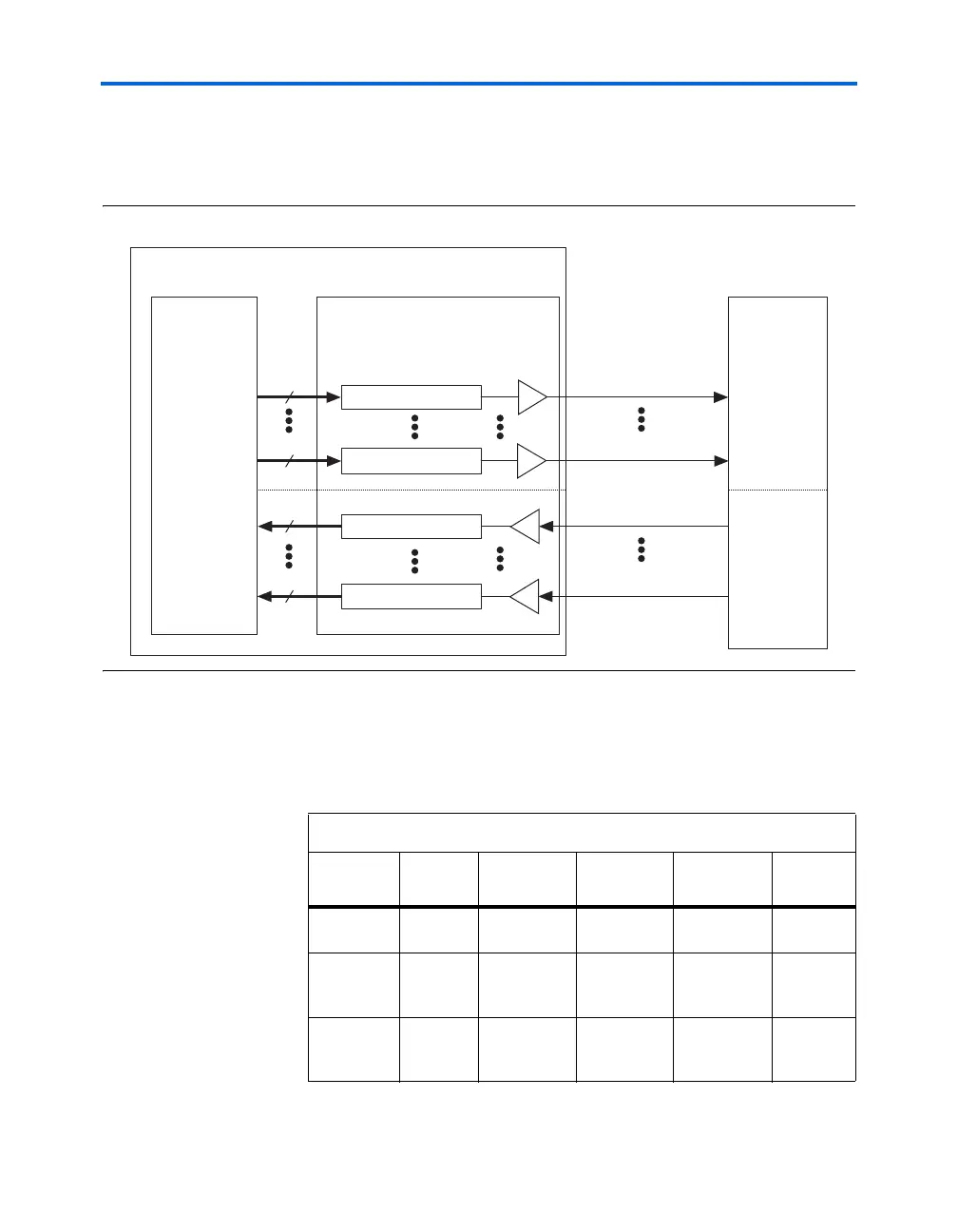

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

information on XAUI support in Section II, Stratix GX Transceiver User

Guide of the Stratix GX Device Handbook, Volume 2. Figure 8–16 shows how

XAUI is implemented.

Figure 8–16. Stratix GX XAUI Implementation

I/O

Characteristics

for XSBI, XGMII

& XAUI

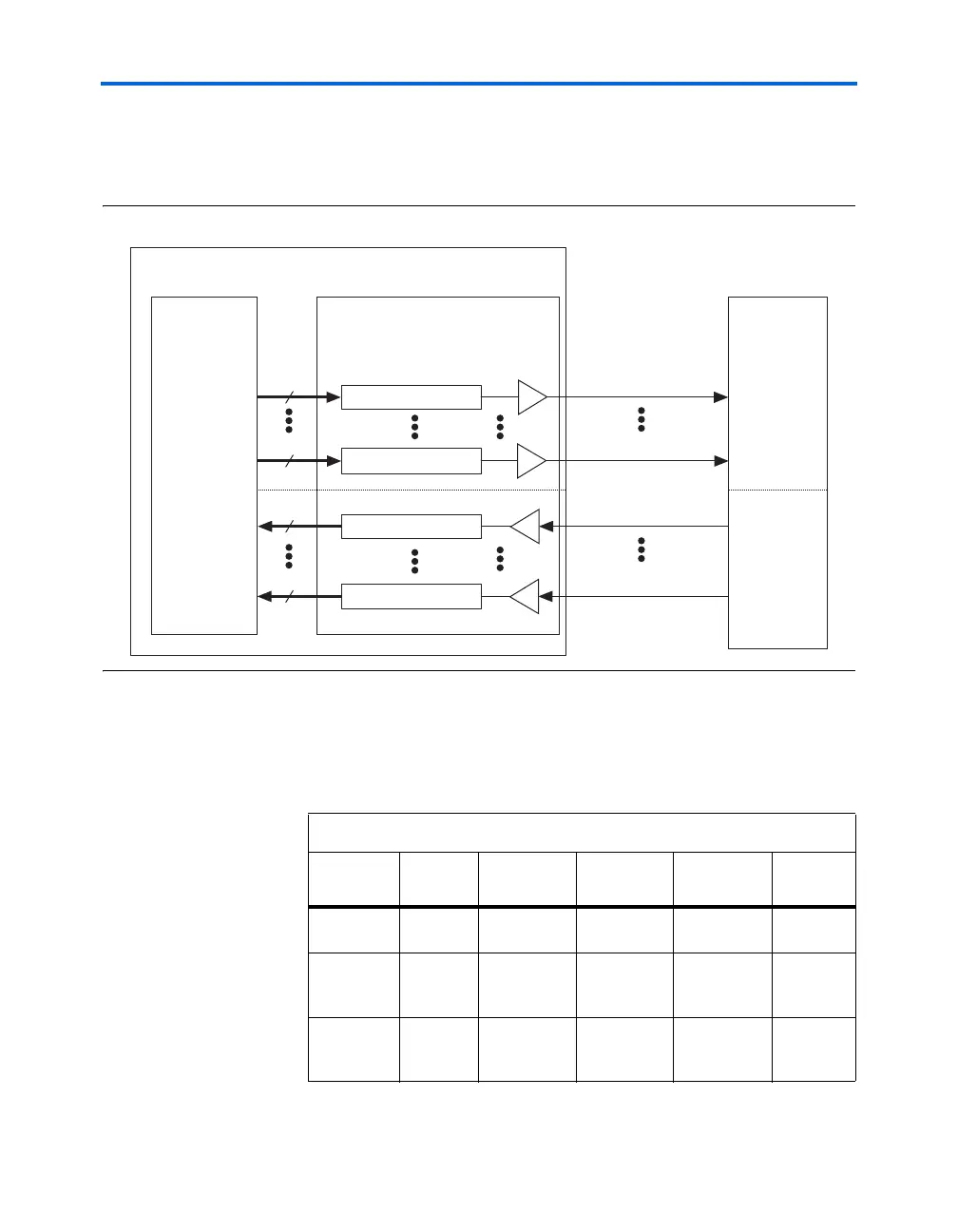

The three interfaces of 10-Gigabit Ethernet (XSBI, XGMII, and XAUI) each

have different rates and I/O standards. Table 8–9 shows the

characteristics for each interface.

TX_D[0]

8

8

CH0

CH0

RX_D[0]

Stratix GX XAUI

CDR Tx

TX_D[3]

8

CH3

CDR Tx

8

CH3

RX_D[3]

PCS

Receiver

Transmitter

CDR Rx

CDR Rx

3.125 Gbps

Stratix GX

Logic Array

Table 8–9. 10-Gigabit Ethernet Interfaces Characteristics

Interface Width

Clock Rate

(MHz)

Data Rate

Per Channel

Clocking

Scheme

I/O Type

XGMII 32 156.25 312.5 Mbps DDR source

synchronous

1.5-V

HSTL

XSBI 16 644.5 or

622.08

644.5 or

622.08

Mbps

SDR source

synchronous

LVDS

XAUI 4 None 3.125 Gbps Clock data

recovery

(CDR)

1.5-V

PCML

Loading...

Loading...