9–4 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Introduction

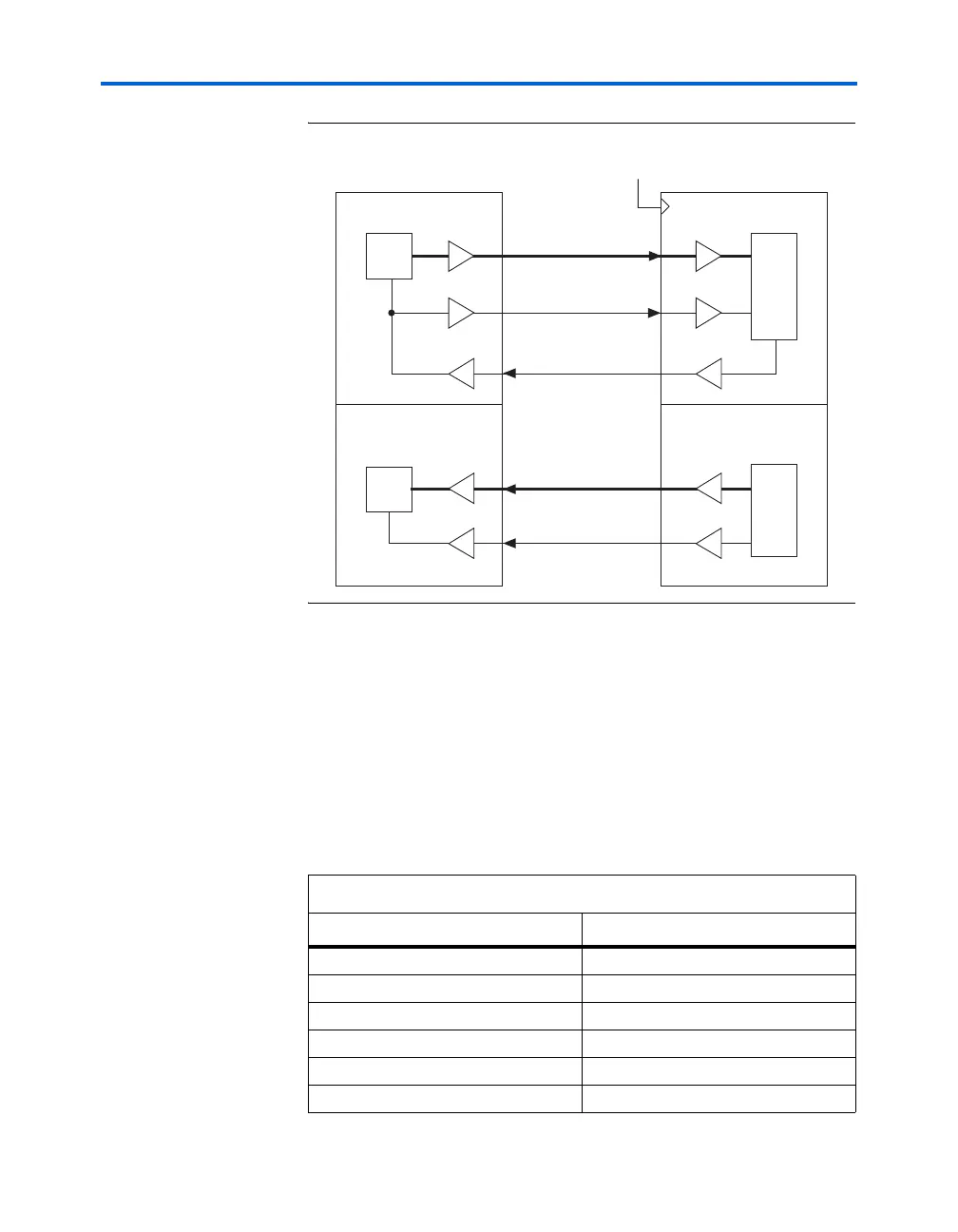

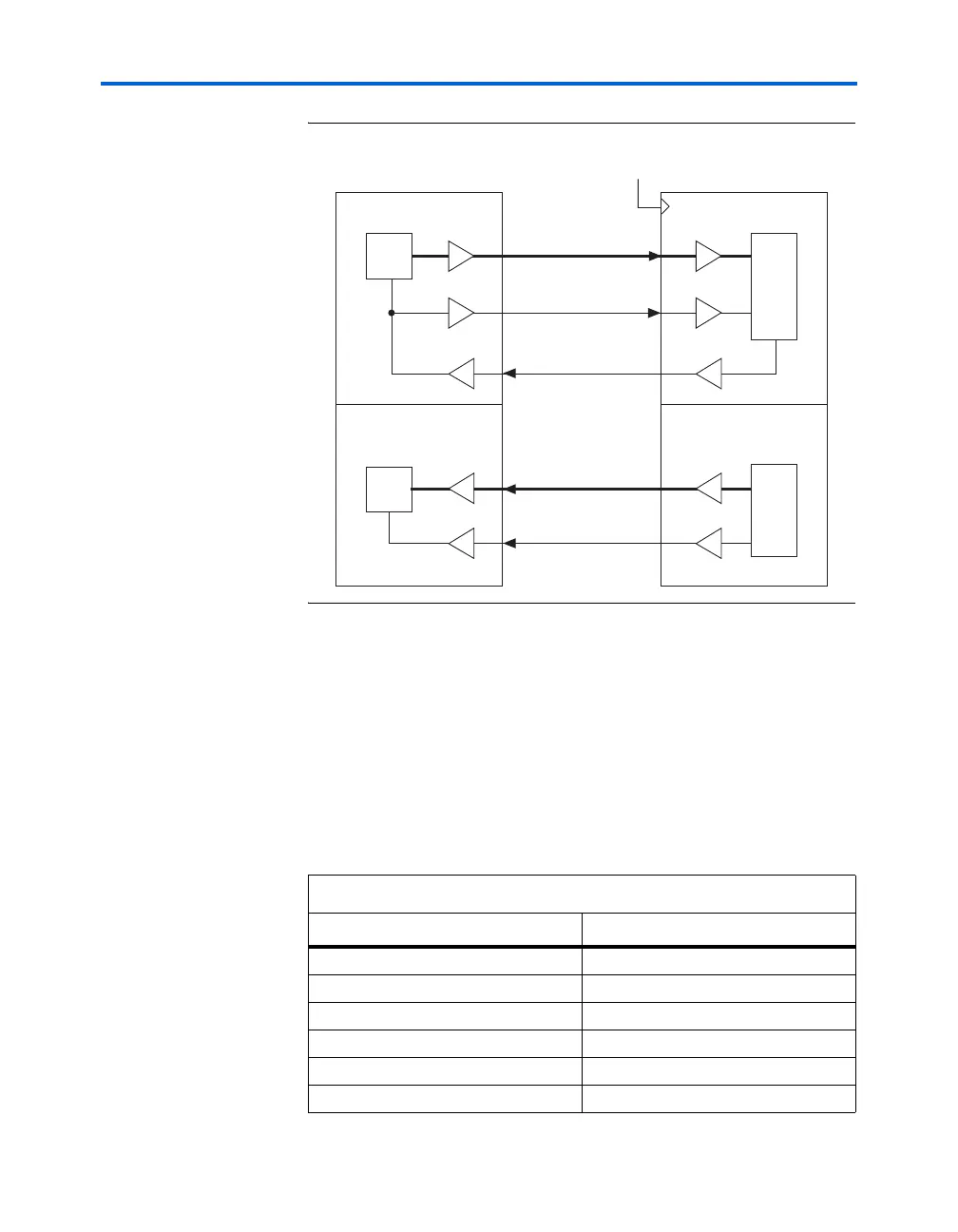

Figure 9–3. SFI-4 Interface Signals

The framer transmits outbound data via TXDATA[15..0] and is

received at the SERDES using TXCLK. TXCLK is derived from

TXCLK_SRC, which is provided by the OC-192 SERDES. The framer

receives incoming data on RXDATA[15..0] from the OC-192 SERDES.

The data received is latched on the rising edge of RXCLK. Table 9–1

provides the data rates and clock frequencies specified by SFI-4. The

modes of TXCLK are specified by the SFI-4 standard. In required mode

(622 MHz clock mode or ×1 mode), TXCLK should run at 622.08 MHz. In

optional mode (311 MHz clock mode or × 2 mode), TXCLK should run at

311.04 MHz.

Table 9–1. SFI-4 Interface Data Rates & Clock Frequencies

Signal Performance

TXDATA[15..0]

622.08 Mbps

TXCLK

622.08 MHz or 311.04 MHz

TXCLK_SRC

622.08 MHz

RXDATA[15..0]

622.08 Mbps

RXCLK

622.08 MHz

REFCLK

622.08 MHz

SONET Framer

Transmitter

OC-192 SERDES

Transmitter

TXDATA[15..0]

TXCLK

TXCLK_SRC

RXDATA[15..0]

RXCLK

SONET Framer

Receiver

Recovered Clock

Receiver

REFCLK

Loading...

Loading...