11–20 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Configuration Schemes

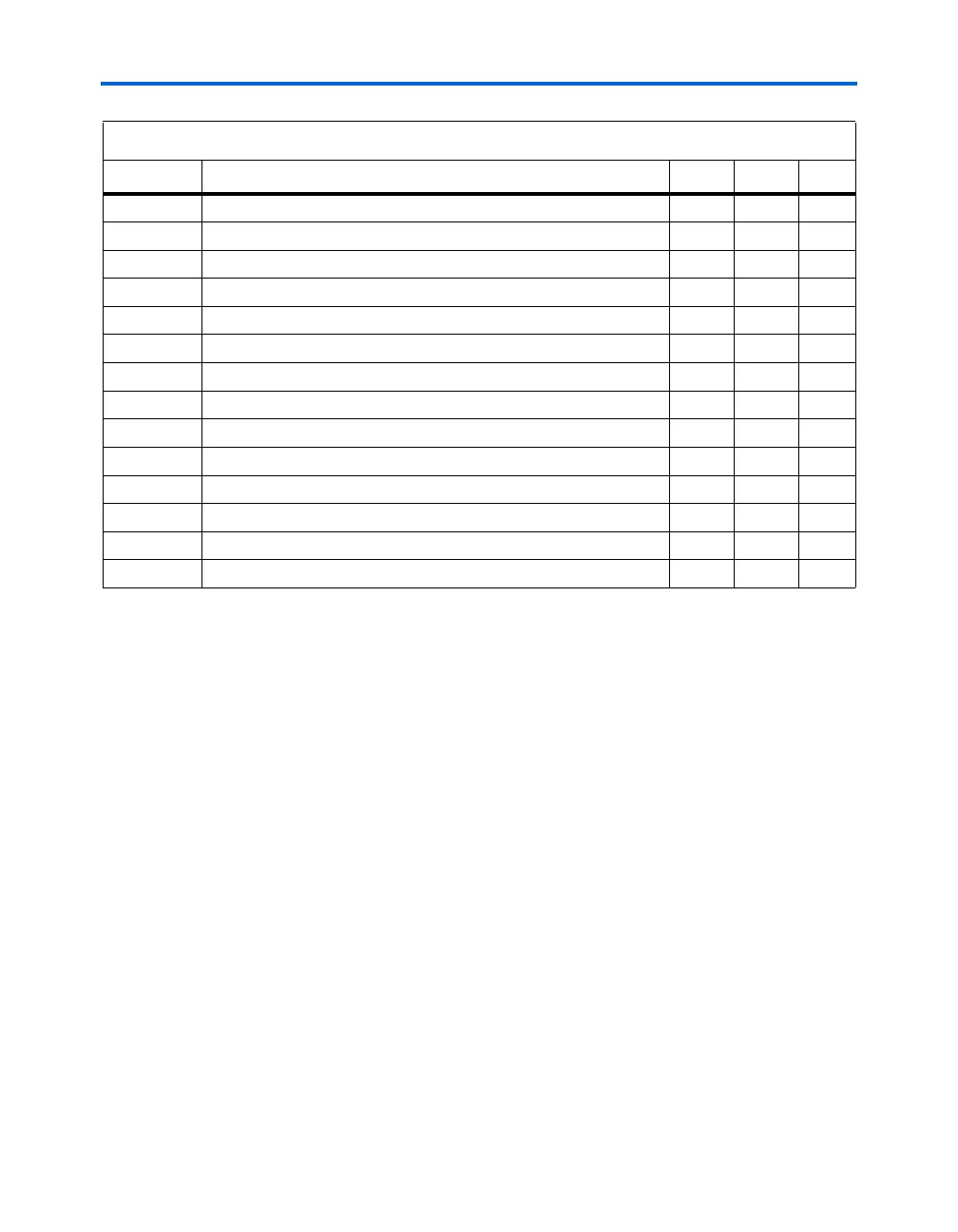

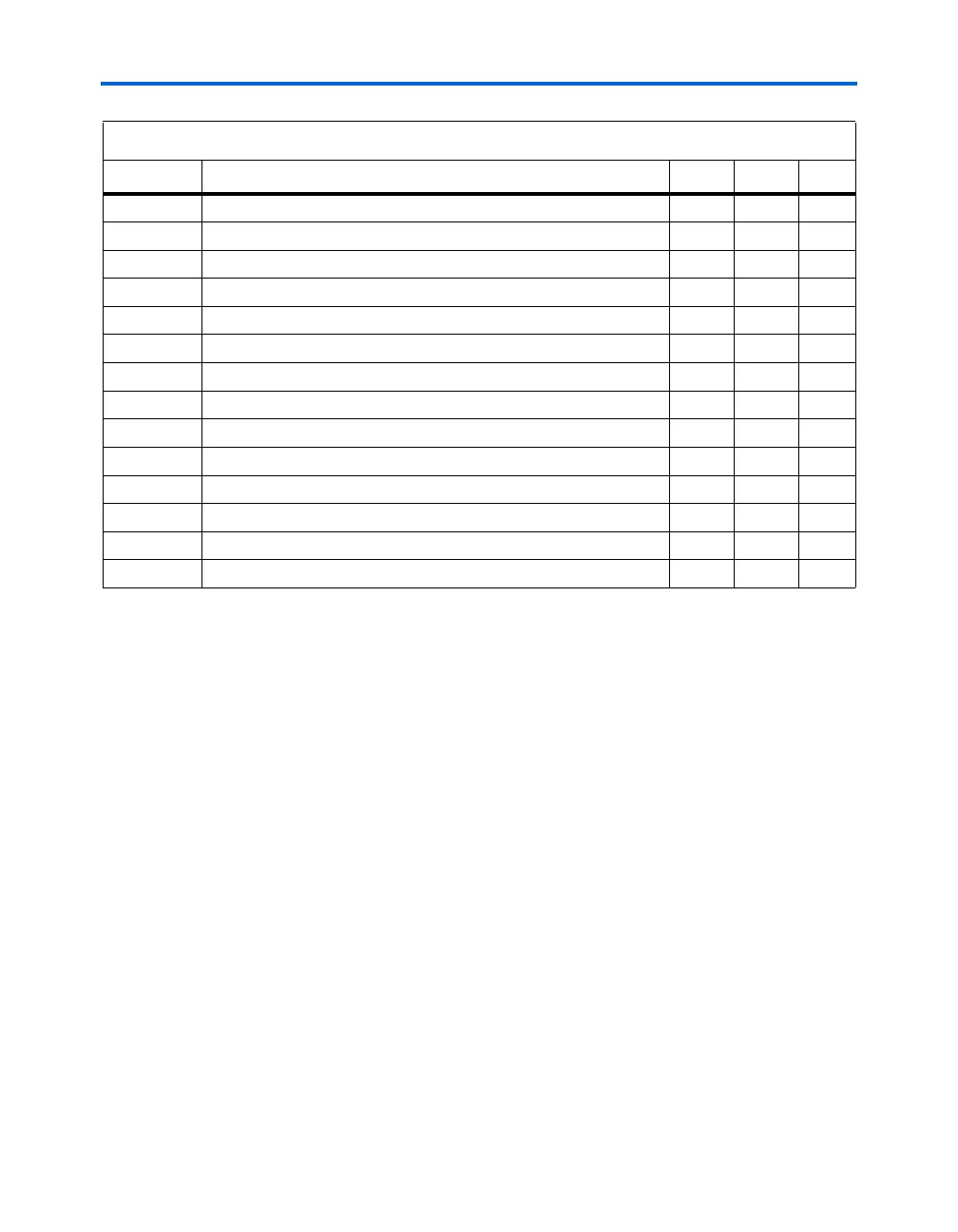

Table 11–8. PS Timing Parameters for Stratix & Stratix GX Devices

Symbol Parameter Min Max Units

t

CF2CD

nCONFIG low to CONF_DONE low

800 ns

t

CF2ST0

nCONFIG low to nSTATUS low

800 ns

t

CF2ST1

nCONFIG high to nSTATUS high

40 (2) µs

t

CFG

nCONFIG low pulse width

40 µs

t

STATUS

nSTATUS low pulse width

10 40 (2) µs

t

CF2CK

nCONFIG high to first rising edge on DCLK

40 µs

t

ST2CK

nSTATUS high to first rising edge on DCLK

1µs

t

DSU

Data setup time before rising edge on DCLK

7ns

t

DH

Data hold time after rising edge on DCLK

0ns

t

CH

DCLK high time

4ns

t

CL

DCLK low time

4ns

t

CLK

DCLK period

10 ns

f

MAX

DCLK maximum frequency

100 MHz

t

CD2UM

CONF_DONE high to user mode (1)

620µs

Notes to Ta b le 11 – 8:

(1) The minimum and maximum numbers apply only if the internal oscillator is chosen as the clock source for starting

up the device. If the clock source is CLKUSR, multiply the clock period by 136 to obtain this value.

(2) This value is obtainable if users do not delay configuration by extending the nSTATUS low pulse width.

Loading...

Loading...