11–52 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

Device Configuration Pins

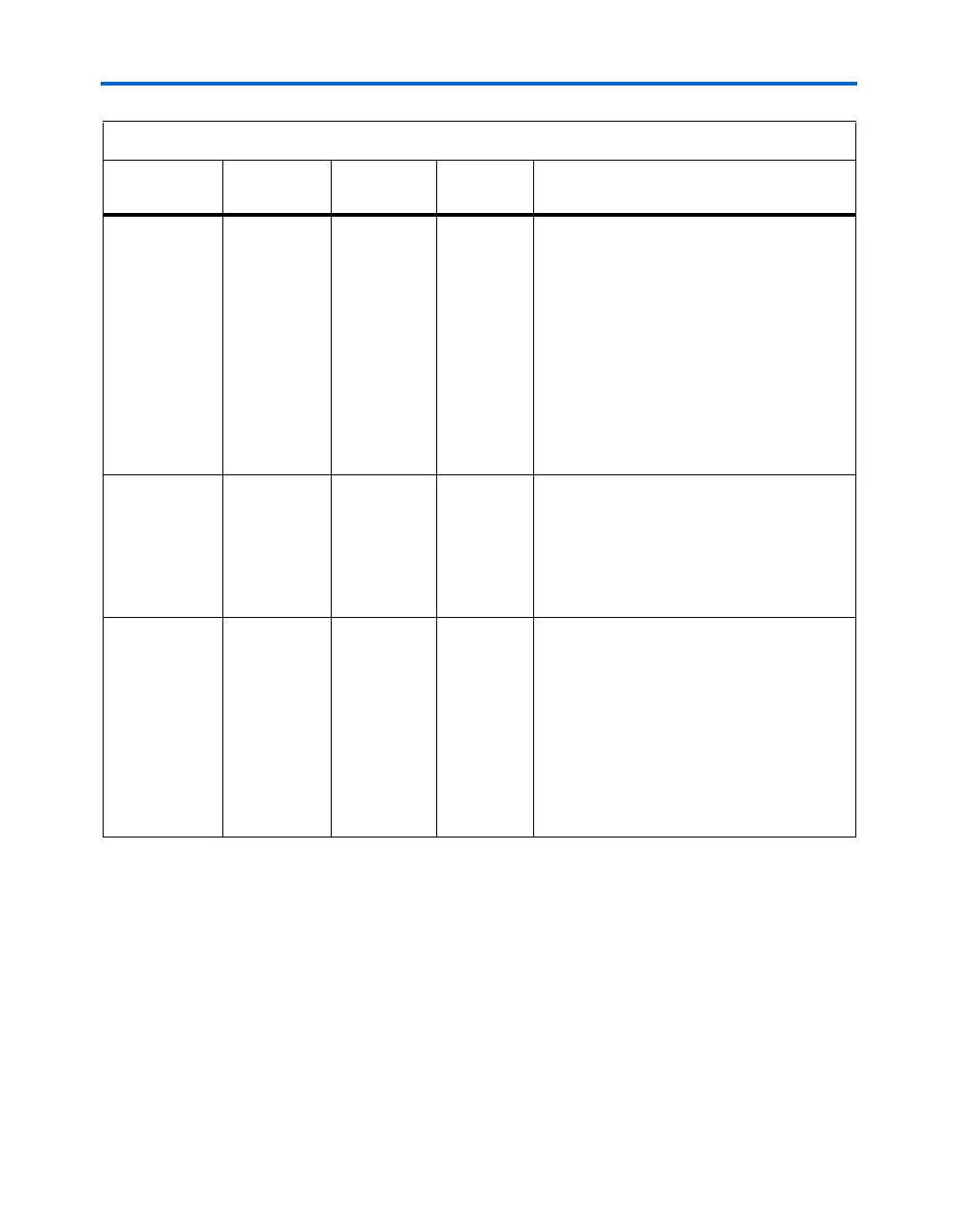

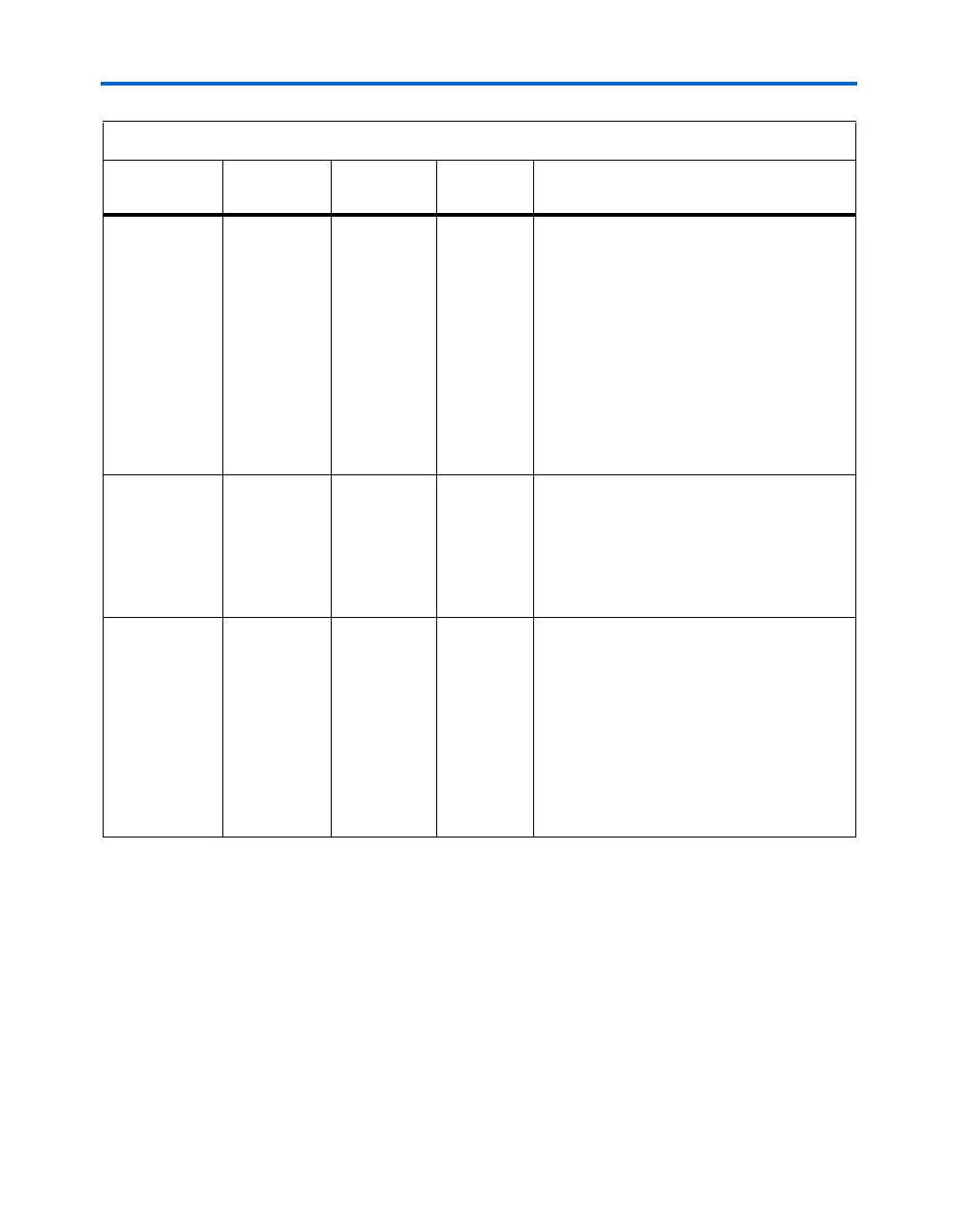

nIO_PULLUP

N/A All Input Dedicated input that chooses whether the

internal pull-ups on the user I/Os and dual-

purpose I/Os (

DATA[7..0], nWS, nRS,

RDYnBSY, nCS, CS, RUnLU, PGM[], CLKUSR,

INIT_DONE, DEV_OE, DEV_CLR) are on or

off before and during configuration. A logic high

(1.5-V, 1.8-V, 2.5-V, 3.3-V) turns off the weak

internal pull-ups, while a logic low turns them

on.

The

nIO_PULLUP input buffer is powered by

V

CCINT

and has an internal 2.5 kΩ pull-down

resistor that is always active.

MSEL[2..0]

N/A All Input 3-bit configuration input that sets the Stratix or

Stratix GX device configuration scheme. See

Table 11–2 for the appropriate connections.

These pins can be connected to V

CCIO

of the

I/O bank they reside in or ground. This pin uses

Schmitt trigger input buffers.

nCONFIG

N/A All Input Configuration control input. Pulling this pin low

during user-mode causes the FPGA to lose its

configuration data, enter a reset state, tri-state

all I/O pins. Returning this pin to a logic high

level initiates a reconfiguration.

If your configuration scheme uses an

enhanced configuration device or EPC2

device,

nCONFIG can be tied directly to V

CC

or

to the configuration device’s

nINIT_CONF

pin. This pin uses Schmitt trigger input buffers.

Table 11–15. Dedicated Configuration Pins on the Stratix or Stratix GX Device (Part 2 of 8)

Pin Name User Mode

Configuration

Scheme

Pin Type Description

Loading...

Loading...