11–56 Altera Corporation

Stratix Device Handbook, Volume 2 July 2005

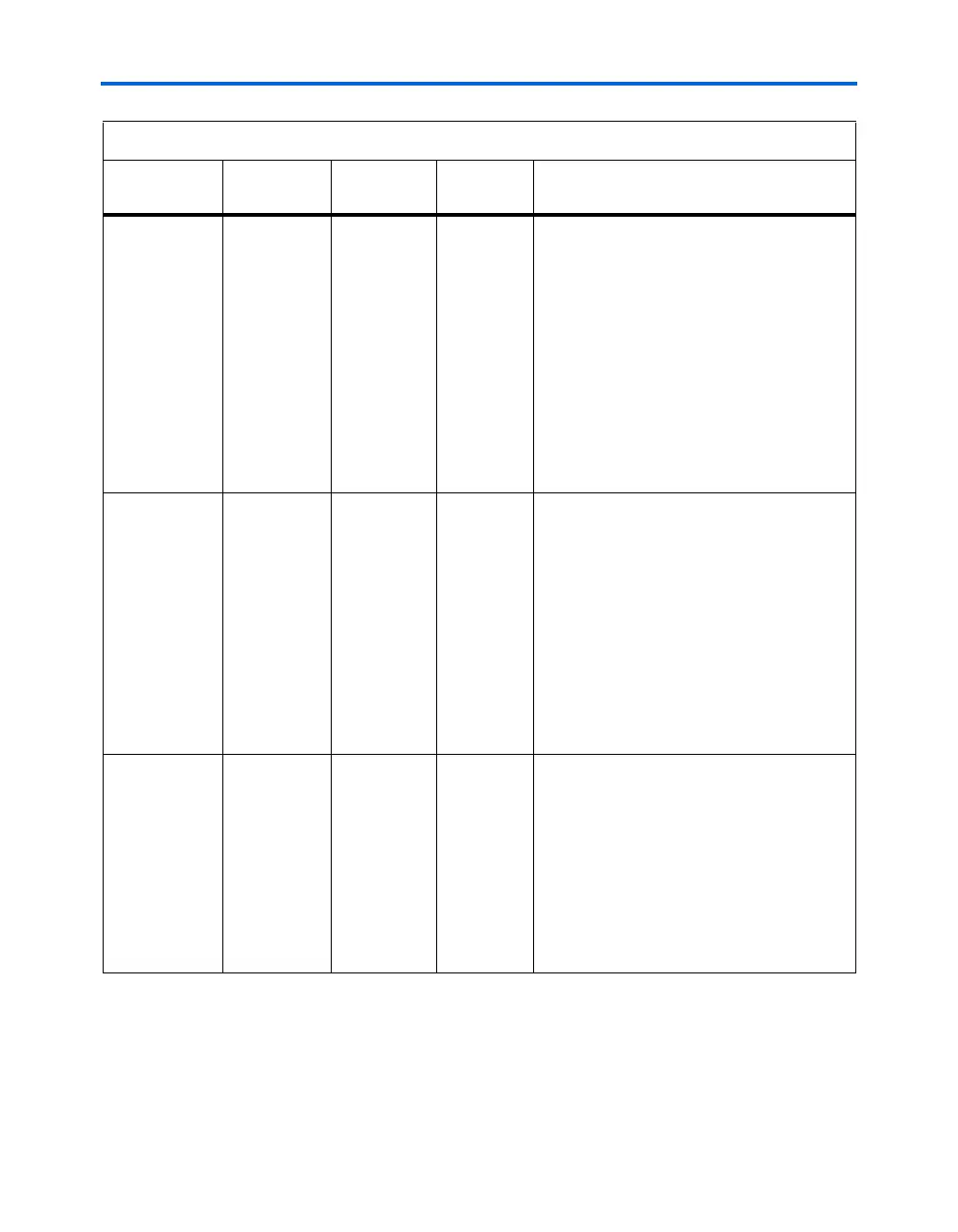

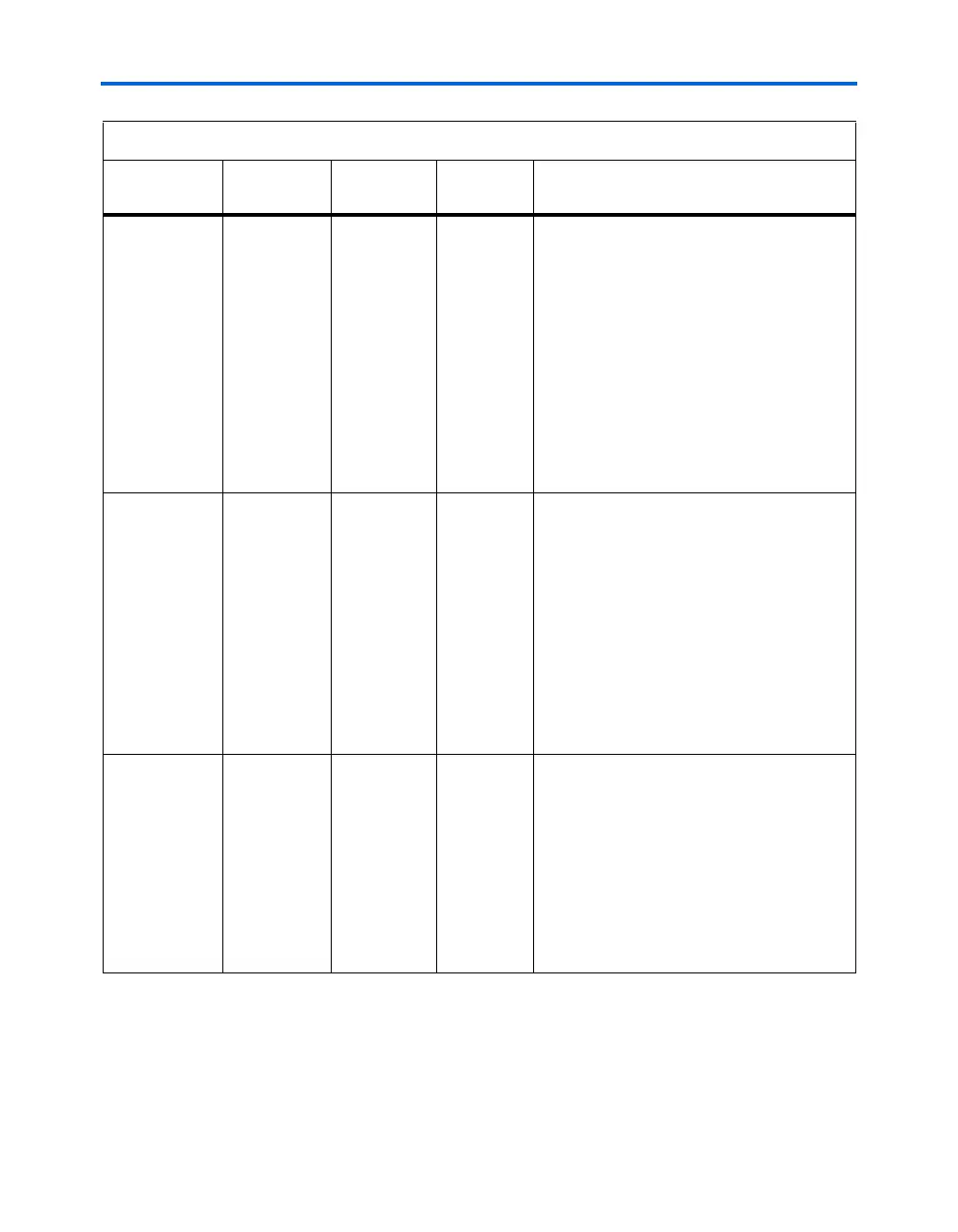

Device Configuration Pins

DATA[7..1]

I/O Parallel

configuration

schemes

(FPP and

PPA)

Inputs Data inputs. Byte-wide configuration data is

presented to the target device on

DATA[7..0]. The V

IH

and V

IL

levels for

these pins are dependent on the V

CCIO

of the

I/O banks that they reside in.

In serial configuration schemes, they function

as user I/Os during configuration, which means

they are tri-stated.

After PPA or FPP configuration,

DATA[7..1]

are available as a user I/Os and the state of

these pin depends on the Dual-Purpose Pin

settings.

DATA7

I/O PPA Bidirectional

In the PPA configuration scheme, the

DATA7

pin presents the

RDYnBSY signal after the nRS

signal has been strobed low. The V

IL

and V

IL

levels for this pin are dependent on the V

CCIO

of the I/O bank that it resides in.

In serial configuration schemes, it functions as

a user I/O during configuration, which means it

is tri-stated.

After PPA configuration,

DATA7 is available as

a user I/O and the state of this pin depends on

the Dual-Purpose Pin settings.

nWS

I/O PPA Input Write strobe input. A low-to-high transition

causes the device to latch a byte of data on the

DATA[7..0] pins.

In non-PPA schemes, it functions as a user I/O

during configuration, which means it is tri-

stated.

After PPA configuration,

nWS is available as a

user I/O and the state of this pin depends on

the Dual-Purpose Pin settings.

Table 11–15. Dedicated Configuration Pins on the Stratix or Stratix GX Device (Part 6 of 8)

Pin Name User Mode

Configuration

Scheme

Pin Type Description

Loading...

Loading...