UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 245 of 523

NXP Semiconductors

UM10462

Chapter 12: LPC11U3x/2x/1x USART

12.5.3 USART Divisor Latch LSB and MSB Registers (when DLAB = 1)

The USART Divisor Latch is part of the USART Baud Rate Generator and holds the value

used (optionally with the Fractional Divider) to divide the UART_PCLK clock in order to

produce the baud rate clock, which must be the multiple of the desired baud rate that is

specified by the Oversampling Register (typically 16X). The DLL and DLM registers

together form a 16-bit divisor. DLL contains the lower 8 bits of the divisor and DLM

contains the higher 8 bits. A zero value is treated like 0x0001. The Divisor Latch Access

Bit (DLAB) in the LCR must be one in order to access the USART Divisor Latches. Details

on how to select the right value for DLL and DLM can be found in Section 12.5.14

.

12.5.4 USART Interrupt Enable Register (when DLAB = 0)

The IER is used to enable the various USART interrupt sources.

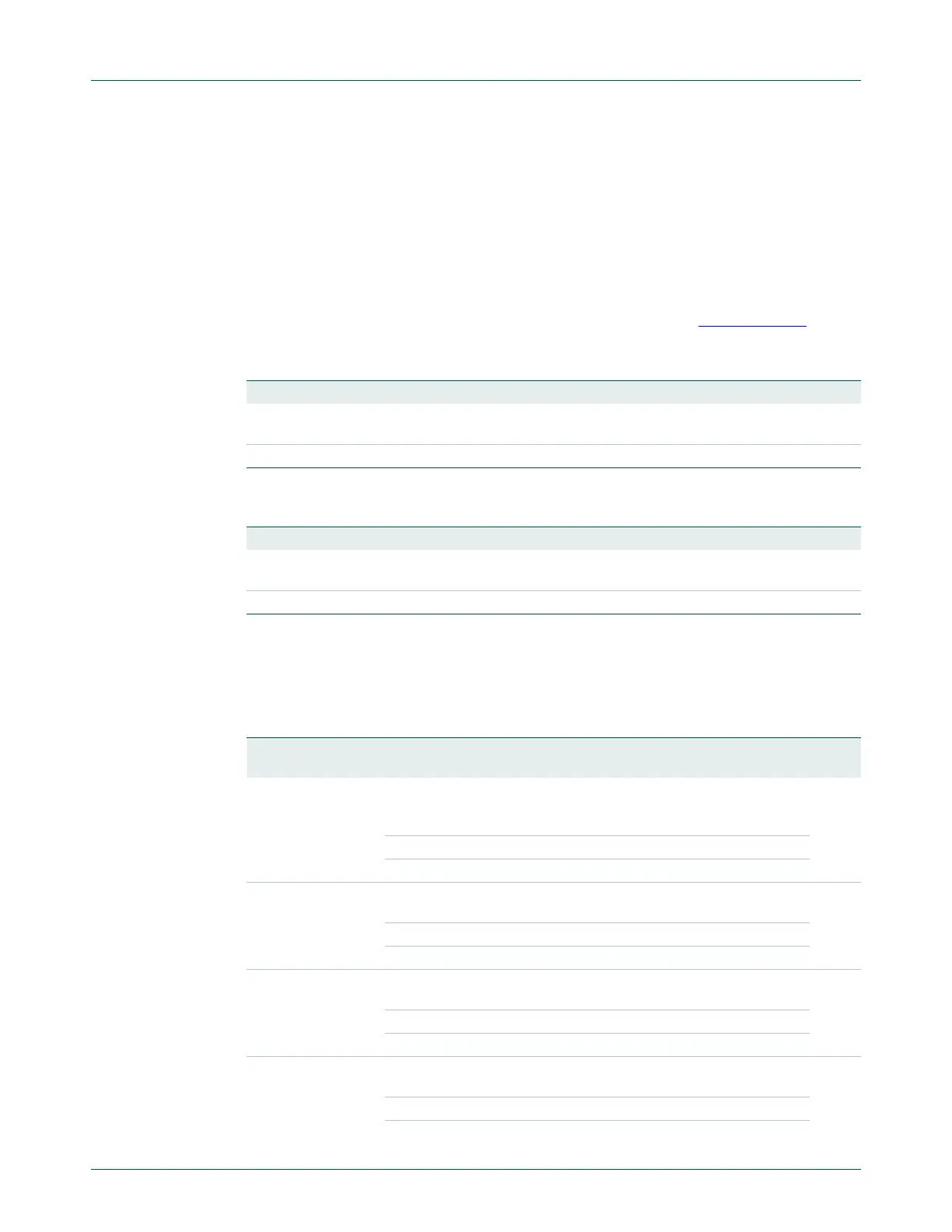

Table 232. USART Divisor Latch LSB Register when DLAB = 1 (DLL - address 0x4000 8000)

bit description

Bit Symbol Description Reset value

7:0 DLLSB The USART Divisor Latch LSB Register, along with the DLM

register, determines the baud rate of the USART.

0x01

31:8 - Reserved -

Table 233. USART Divisor Latch MSB Register when DLAB = 1 (DLM - address 0x4000 8004)

bit description

Bit Symbol Description Reset value

7:0 DLMSB The USART Divisor Latch MSB Register, along with the DLL

register, determines the baud rate of the USART.

0x00

31:8 - Reserved -

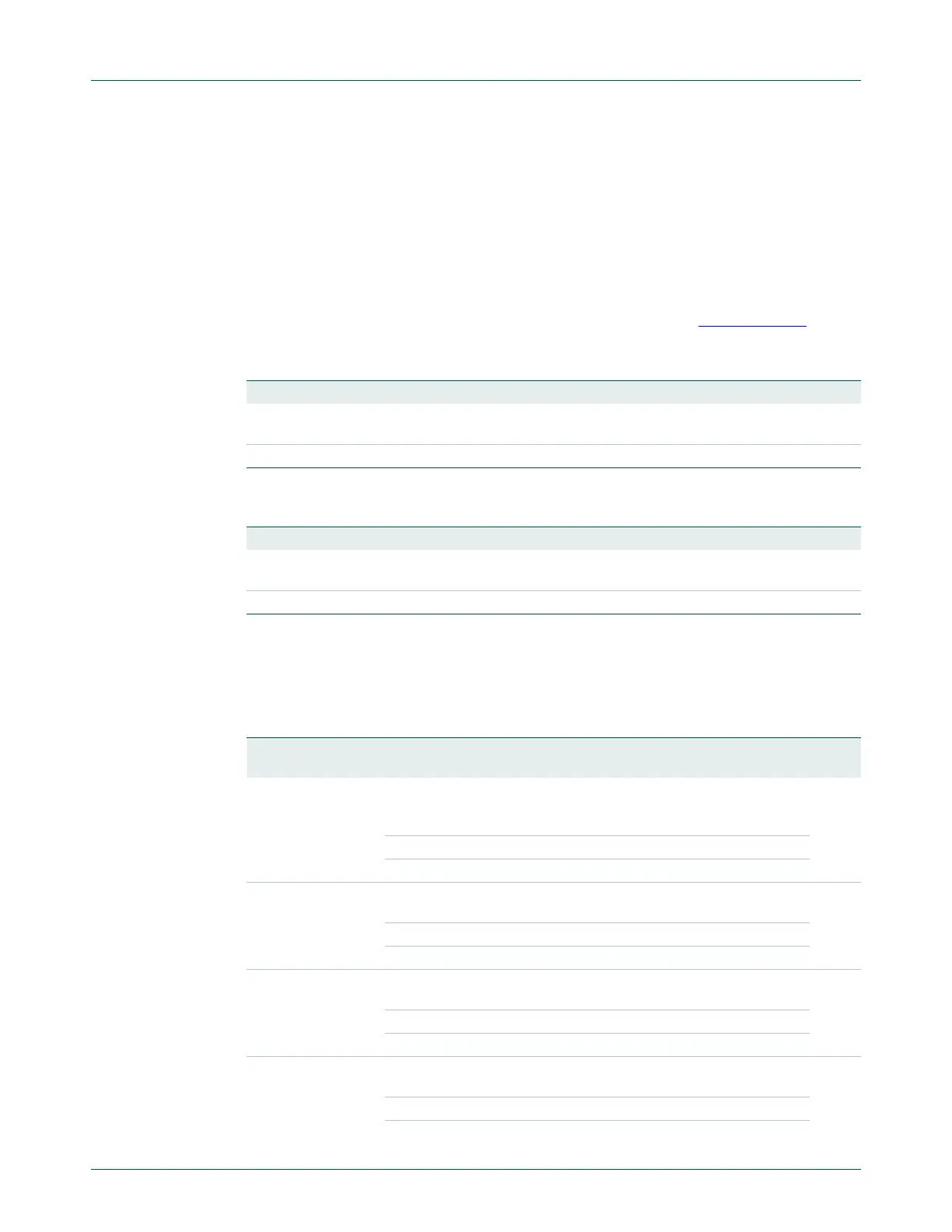

Table 234. USART Interrupt Enable Register when DLAB = 0 (IER - address 0x4000 8004) bit

description

Bit Symbol Value Description Reset

value

0 RBRINTEN RBR Interrupt Enable. Enables the Receive Data Available

interrupt. It also controls the Character Receive Time-out

interrupt.

0

0 Disable the RDA interrupt.

1 Enable the RDA interrupt.

1 THREINTEN THRE Interrupt Enable. Enables the THRE interrupt. The

status of this interrupt can be read from LSR[5].

0

0 Disable the THRE interrupt.

1 Enable the THRE interrupt.

2 RLSINTEN Enables the Receive Line Status interrupt. The status of

this interrupt can be read from LSR[4:1].

-

0 Disable the RLS interrupt.

1 Enable the RLS interrupt.

3 MSINTEN Enables the Modem Status interrupt. The components of

this interrupt can be read from the MSR.

0 Disable the MS interrupt.

1 Enable the MS interrupt.

Loading...

Loading...