UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 169 of 523

NXP Semiconductors

UM10462

Chapter 9: LPC11U3x/2x/1x GPIO

9.6.4.2 Group interrupts

In this interrupt facility, an interrupt can be requested for each port, based on any selected

subset of pins within each port. The pins that contribute to each port interrupt are selected

by 1s in the port’s Enable register, and an interrupt polarity can be selected for each pin in

the port’s Polarity register. The level on each pin is exclusive-ORed with its polarity bit and

the result is ANDed with its enable bit, and these results are then inclusive-ORed among

all the pins in the port, to create the port’s raw interrupt request.

The raw interrupt request from each of the two group interrupts is sent to the NVIC, which

can be programmed to treat it as level- or edge-sensitive (see Section 6.4

), or it can be

edge-detected by the wake-up interrupt logic (see Section 3.5.37

).

9.6.5 Recommended practices

The following lists some recommended uses for using the GPIO port registers:

• For initial setup after Reset or re-initialization, write the PORT register(s).

• To change the state of one pin, write a Byte Pin or Word Pin register.

• To change the state of multiple pins at a time, write the SET and/or CLR registers.

• To change the state of multiple pins in a tightly controlled environment like a software

state machine, consider using the NOT register. This can require less write operations

than SET and CLR.

• To read the state of one pin, read a Byte Pin or Word Pin register.

• To make a decision based on multiple pins, read and mask a PORT register.

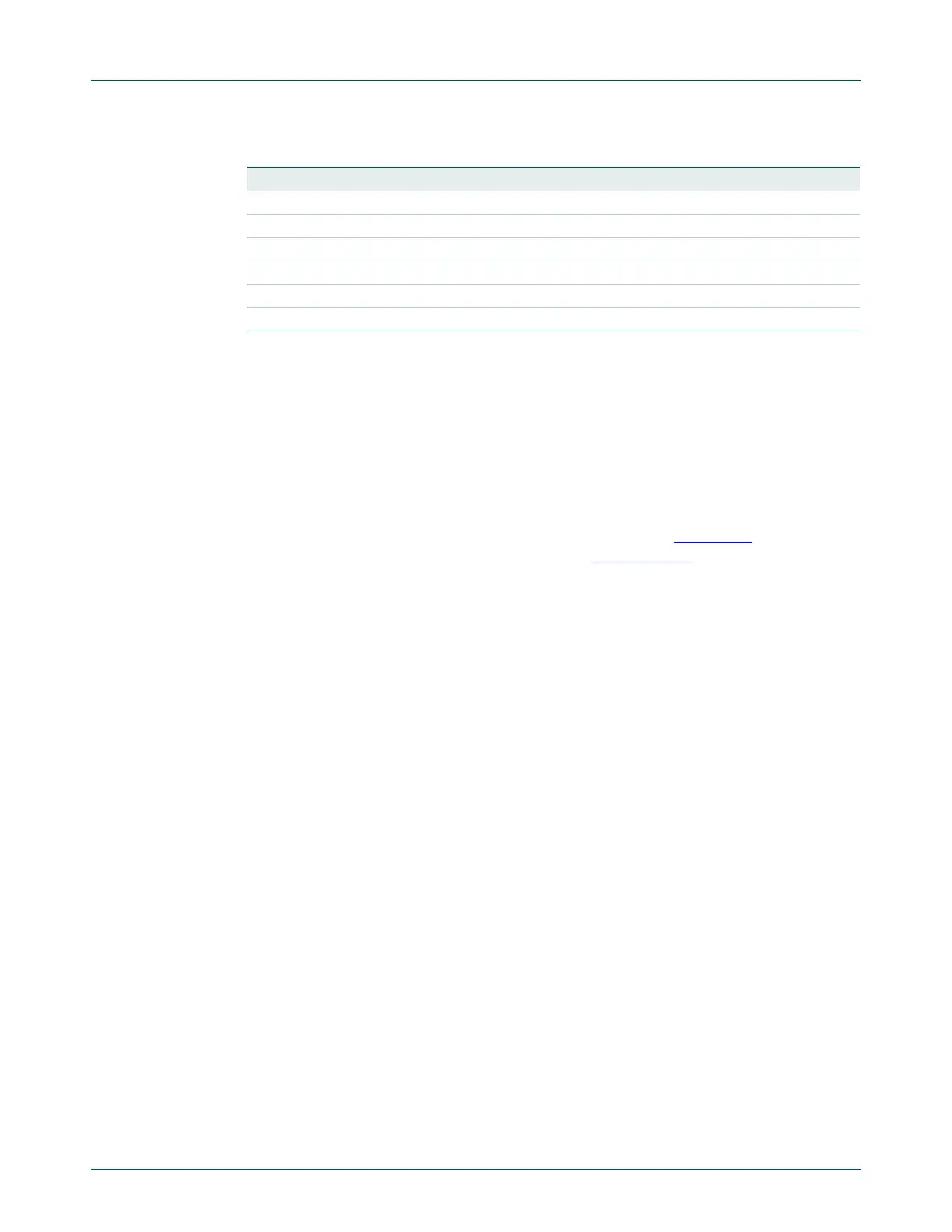

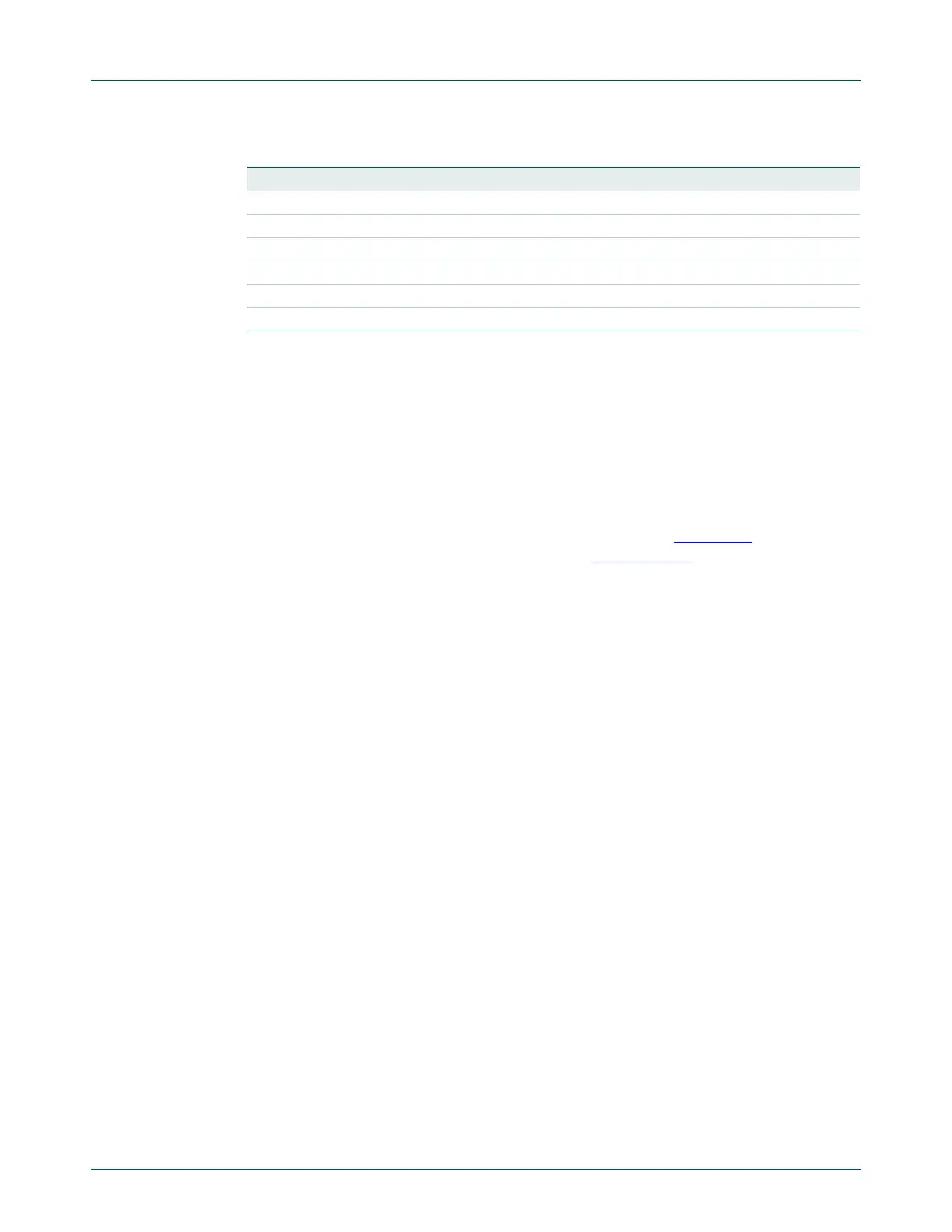

Table 174. Pin interrupt registers for edge- and level-sensitive pins

Name Edge-sensitive function Level-sensitive function

IENR Enables rising-edge interrupts. Enables level interrupts.

SIENR Write to enable rising-edge interrupts. Write to enable level interrupts.

CIENR Write to disable rising-edge interrupts. Write to disable level interrupts.

IENF Enables falling-edge interrupts. Selects active level.

SIENF Write to enable falling-edge interrupts. Write to select high-active.

CIENF Write to disable falling-edge interrupts. Write to select low-active.

Loading...

Loading...