UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 22 of 523

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

3.5.1 System memory remap register

The system memory remap register selects whether the exception vectors are read from

boot ROM, flash, or SRAM. By default, the flash memory is mapped to address 0x0000

0000. When the MAP bits in the SYSMEMREMAP register are set to 0x0 or 0x1, the boot

ROM or RAM respectively are mapped to the bottom 512 bytes of the memory map

(addresses 0x0000 0000 to 0x0000 0200).

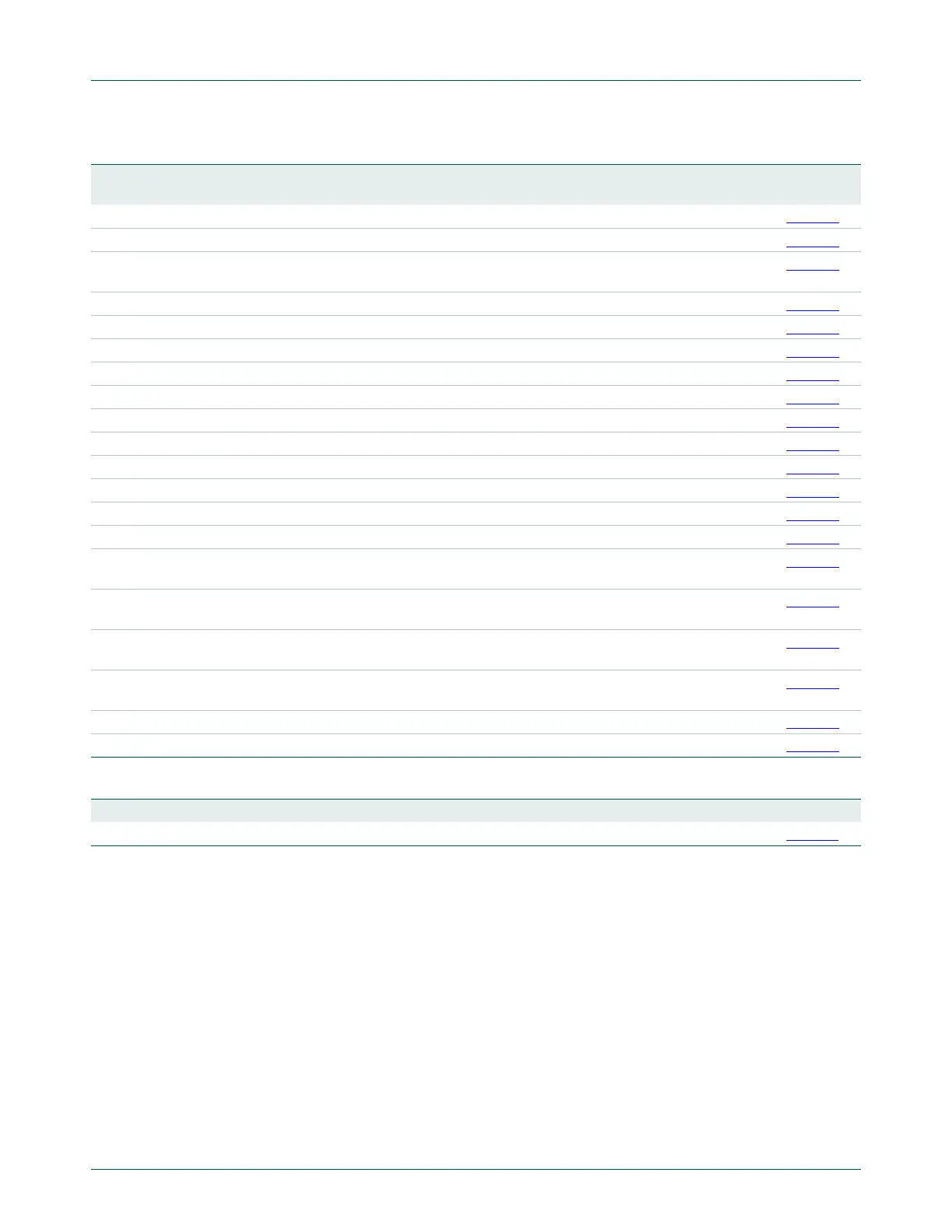

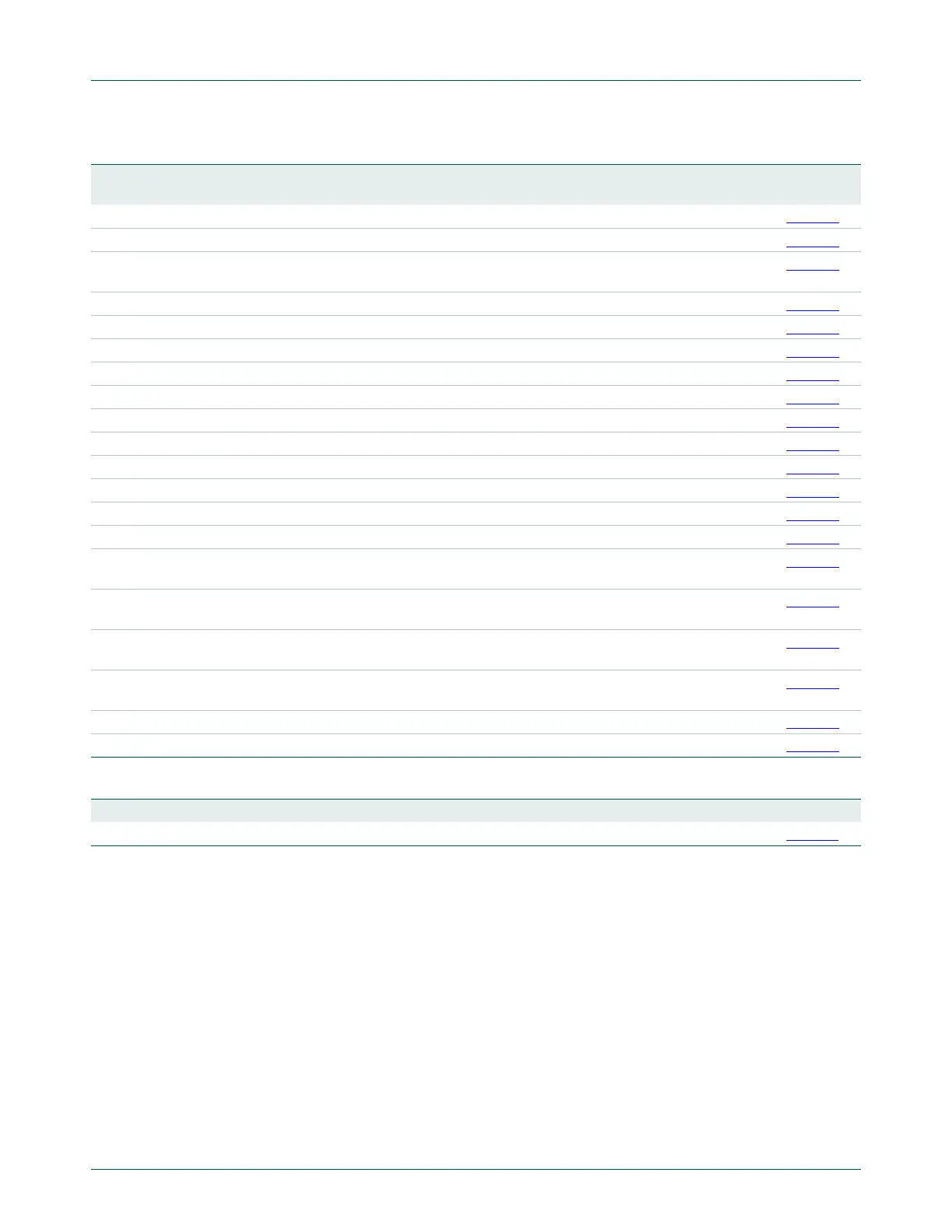

BODCTRL R/W 0x150 Brown-Out Detect 0 0 Table 36

SYSTCKCAL R/W 0x154 System tick counter calibration 0x0 0x4 Table 37

IRQLATENCY R/W 0x170 IRQ delay. Allows trade-off between

interrupt latency and determinism.

0x10 0x10 Ta ble 38

NMISRC R/W 0x174 NMI Source Control 0 0 Table 39

PINTSEL0 R/W 0x178 GPIO Pin Interrupt Select register 0 0 0 Table 40

PINTSEL1 R/W 0x17C GPIO Pin Interrupt Select register 1 0 0 Table 40

PINTSEL2 R/W 0x180 GPIO Pin Interrupt Select register 2 0 0 Table 40

PINTSEL3 R/W 0x184 GPIO Pin Interrupt Select register 3 0 0 Table 40

PINTSEL4 R/W 0x188 GPIO Pin Interrupt Select register 4 0 0 Table 40

PINTSEL5 R/W 0x18C GPIO Pin Interrupt Select register 5 0 0 Table 40

PINTSEL6 R/W 0x190 GPIO Pin Interrupt Select register 6 0 0 Table 40

PINTSEL7 R/W 0x194 GPIO Pin Interrupt Select register 7 0 0 Table 40

USBCLKCTRL R/W 0x198 USB clock control 0 0 Table 41

USBCLKST R 0x19C USB clock status 0x1 0x1 Table 42

STARTERP0 R/W 0x204 Start logic 0 interrupt wake-up enable

register 0

00Table 43

STARTERP1 R/W 0x214 Start logic 1 interrupt wake-up enable

register 1

00Table 44

PDSLEEPCFG R/W 0x230 Power-down states in deep-sleep

mode

0xFFFF 0xFFFF Table 45

PDAWAKECFG R/W 0x234 Power-down states for wake-up from

deep-sleep

0xEDF0 0xEDF0 Table 46

PDRUNCFG R/W 0x238 Power configuration register 0xEDD0 0xEDF0 Table 47

DEVICE_ID R 0x3F4 Device ID part dependent Table 48

Table 5. Register overview: system control block (base address 0x4004 8000) …continued

Name Access Offset Description Reset value Reset value

after boot

Reference

Table 6. Register overview: flash control block (base address 0x4003 C000)

Name Access Offset Description Reset value Reference

FLASHCFG R/W 0x010 Flash read access configuration - Table 49

Loading...

Loading...