UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 70 of 523

NXP Semiconductors

UM10462

Chapter 6: LPC11U3x/2x/1x NVIC

6.5 Register description

See the ARM Cortex-M0+ technical reference manual.

The NVIC registers are located on the ARM private peripheral bus.

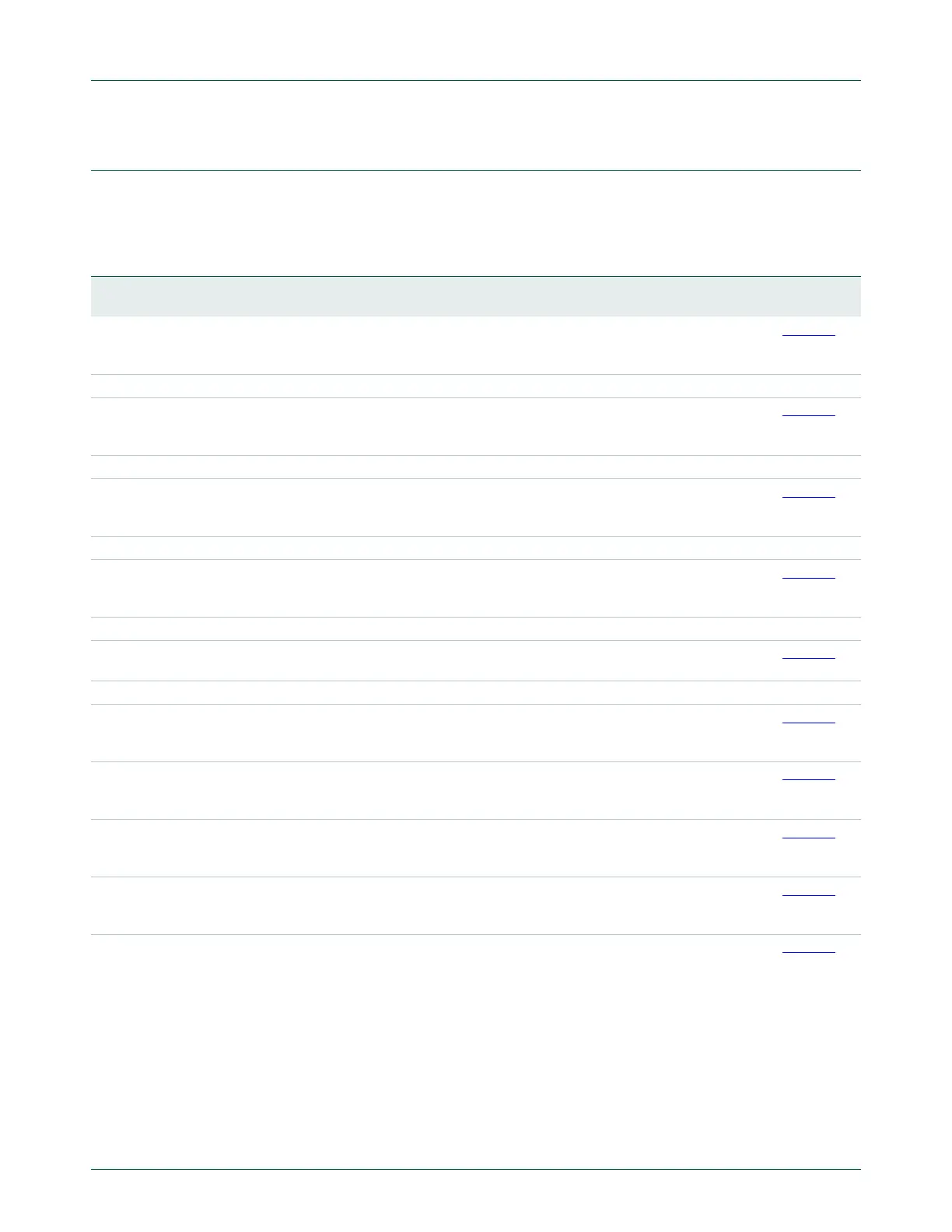

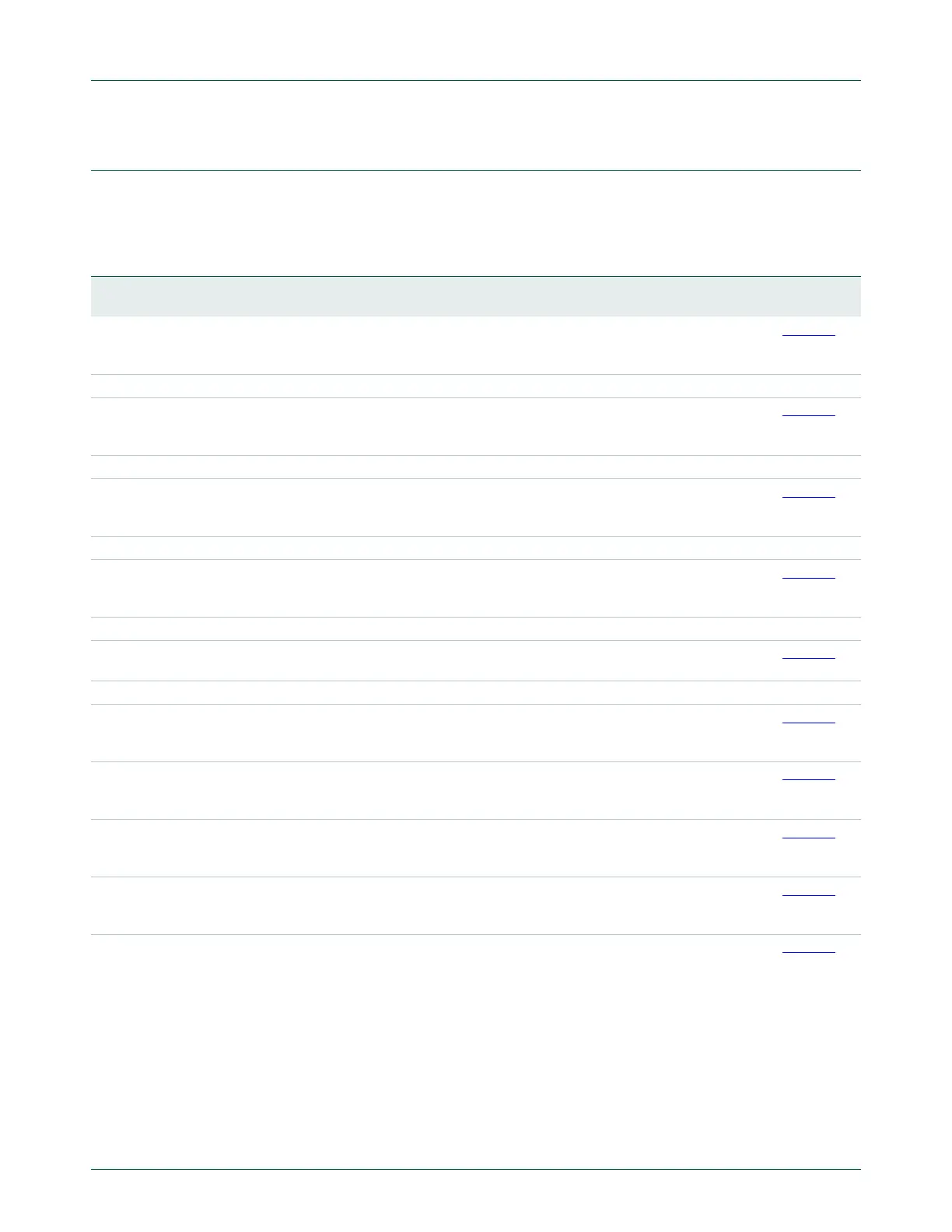

Table 60. Register overview: NVIC (base address 0xE000 E000)

Name Access Address

offset

Description Reset

value

Reference

ISER0 R/W 0x100 Interrupt Set Enable Register 0. This register allows enabling

interrupts and reading back the interrupt enables for specific

peripheral functions.

0 Table 61

- - 0x104 Reserved. - -

ICER0 R/W 0x180 Interrupt Clear Enable Register 0. This register allows disabling

interrupts and reading back the interrupt enables for specific

peripheral functions.

0 Table 62

- - 0x184 Reserved. 0 -

ISPR0 R/W 0x200 Interrupt Set Pending Register 0. This register allows changing the

interrupt state to pending and reading back the interrupt pending

state for specific peripheral functions.

0 Table 63

- - 0x204 Reserved. 0 -

ICPR0 R/W 0x280 Interrupt Clear Pending Register 0. This register allows changing the

interrupt state to not pending and reading back the interrupt pending

state for specific peripheral functions.

0 Table 64

- - 0x284 Reserved. 0 -

IABR0 RO 0x300 Interrupt Active Bit Register 0. This register allows reading the

current interrupt active state for specific peripheral functions.

0 Table 65

- - 0x304 Reserved. 0 -

IPR0 R/W 0x400 Interrupt Priority Registers 0. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 0 to 3.

0 Table 66

IPR1 R/W 0x404 Interrupt Priority Registers 1 This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 4 to 7.

0 Table 67

IPR2 R/W 0x408 Interrupt Priority Registers 2. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 8 to 11.

0 Table 68

IPR3 R/W 0x40C Interrupt Priority Registers 3. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 12 to 15.

0 Table 69

IPR4 R/W 0x410 Interrupt Priority Registers 4. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 12 to 15.

0 Table 70

Loading...

Loading...