UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 225 of 523

NXP Semiconductors

UM10462

Chapter 11: LPC11U3x/2x/1x USB2.0 device controller

11.4.7 Clocking

The LPC11U3x/2x/1x USB device controller has the following clock connections:

• USB main clock: The USB main clock is the 48 MHz +/- 500 ppm clock from the

dedicated USB PLL or the main clock (see Table 28

). If the main clock is used, the

system PLL output must be 48 MHz. The clock source for the USB PLL or the system

PLL must be derived from the system oscillator if the USB is operated in full-speed

mode. For low-speed mode, the IRC is suitable as the clock source.

The USB main clock is used to recover the 12 MHz clock from the USB bus.

• AHB clock: This is the AHB system bus clock. The minimum frequency of the AHB

clock is 6 MHz when the USB device controller is receiving or transmitting USB

packets.

11.5 Pin description

The device controller can access one USB port.

11.6 Register description

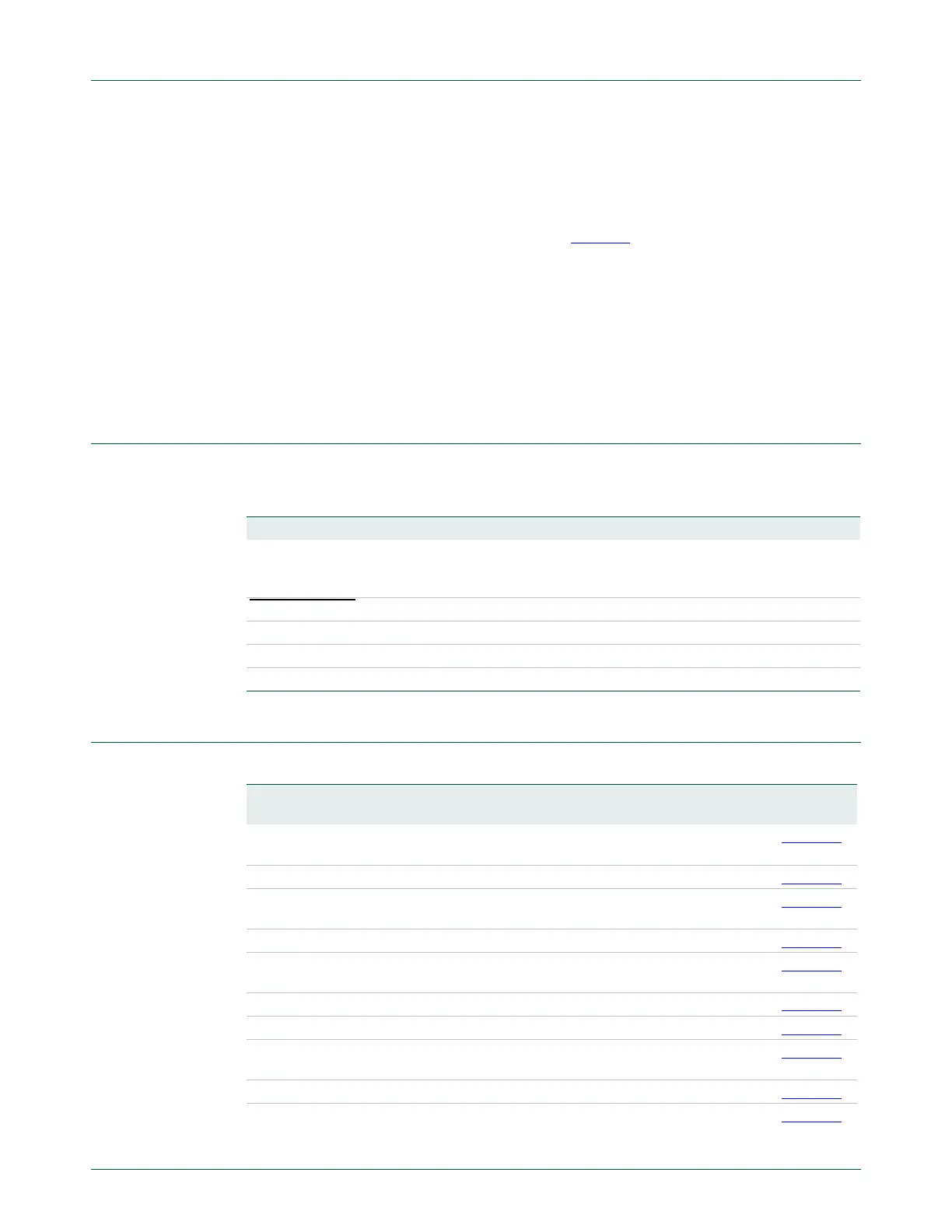

Table 212. USB device pin description

Name Direction Description

V

BUS

IV

BUS

status input. When this function is not enabled

via its corresponding IOCON register, it is driven

HIGH internally.

USB_CONNECT

O SoftConnect control signal.

USB_FTOGGLE O USB 1 ms SoF signal.

USB_DP I/O Positive differential data.

USB_DM I/O Negative differential data.

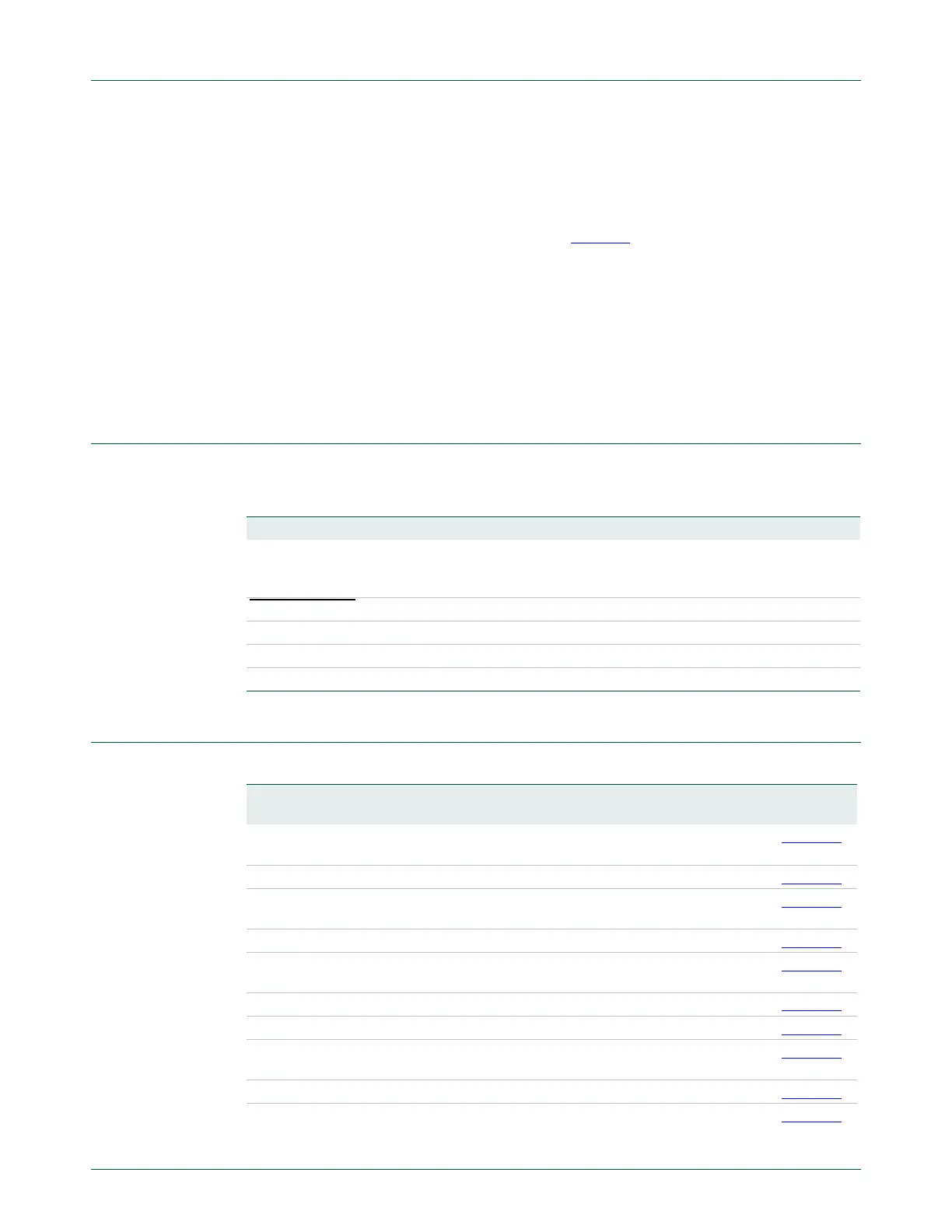

Table 213. Register overview: USB (base address: 0x4008 0000)

Name Access Address

offset

Description Reset

value

Reference

DEVCMDSTAT R/W 0x000 USB Device Command/Status

register

0x00000

800

Table 214

INFO R/W 0x004 USB Info register 0 Table 215

EPLISTSTART R/W 0x008 USB EP Command/Status List

start address

0 Table 216

DATABUFSTART R/W 0x00C USB Data buffer start address 0 Table 217

LPM R/W 0x010 USB Link Power Management

register

0 Table 218

EPSKIP R/W 0x014 USB Endpoint skip 0 Table 219

EPINUSE R/W 0x018 USB Endpoint Buffer in use 0 Table 220

EPBUFCFG R/W 0x01C USB Endpoint Buffer

Configuration register

0 Table 221

INTSTAT R/W 0x020 USB interrupt status register 0 Table 222

INTEN R/W 0x024 USB interrupt enable register 0 Table 223

Loading...

Loading...