UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 77 of 523

NXP Semiconductors

UM10462

Chapter 6: LPC11U3x/2x/1x NVIC

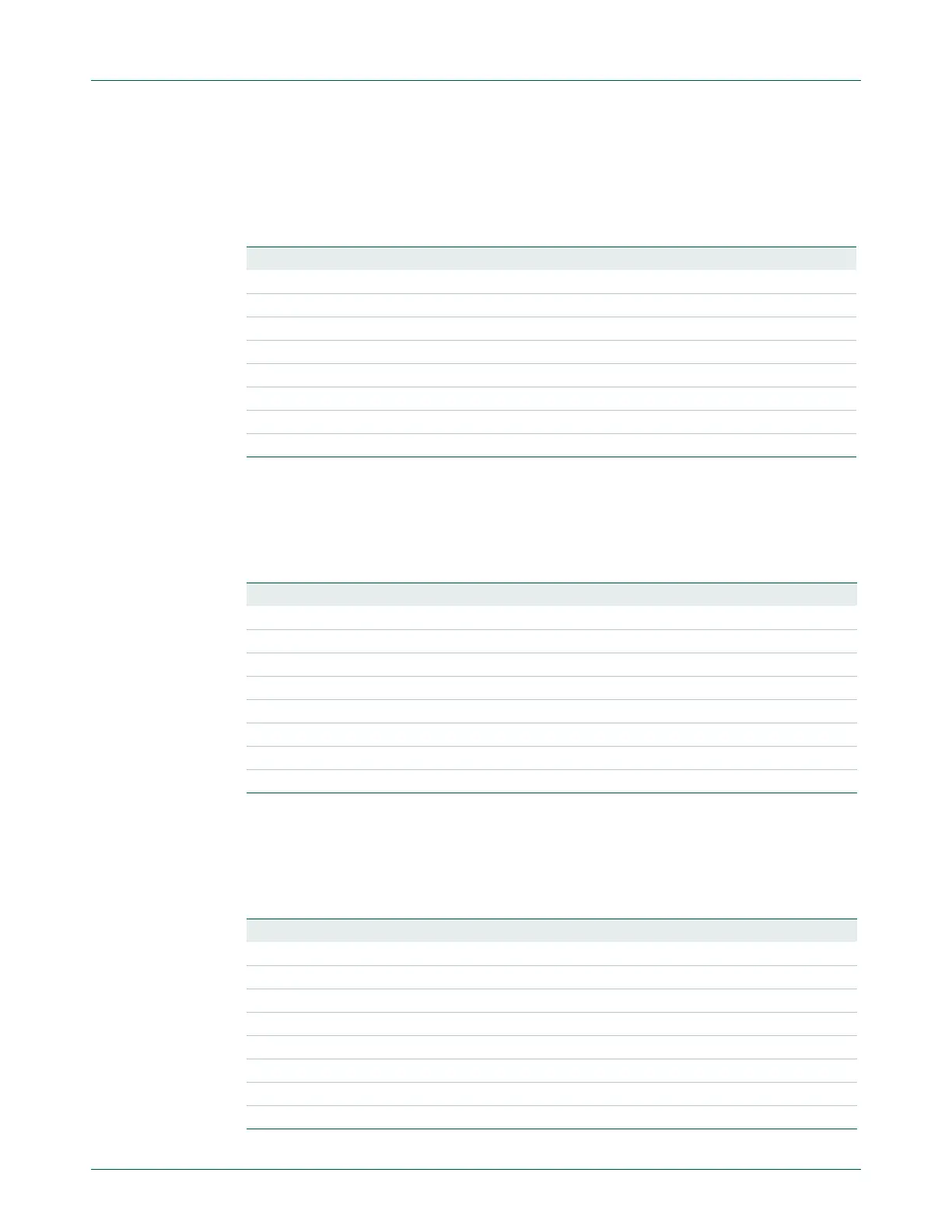

6.5.7 Interrupt Priority Register 1

The IPR1 register controls the priority of four peripheral interrupts. Each interrupt can

have one of 4 priorities, where 0 is the highest priority.

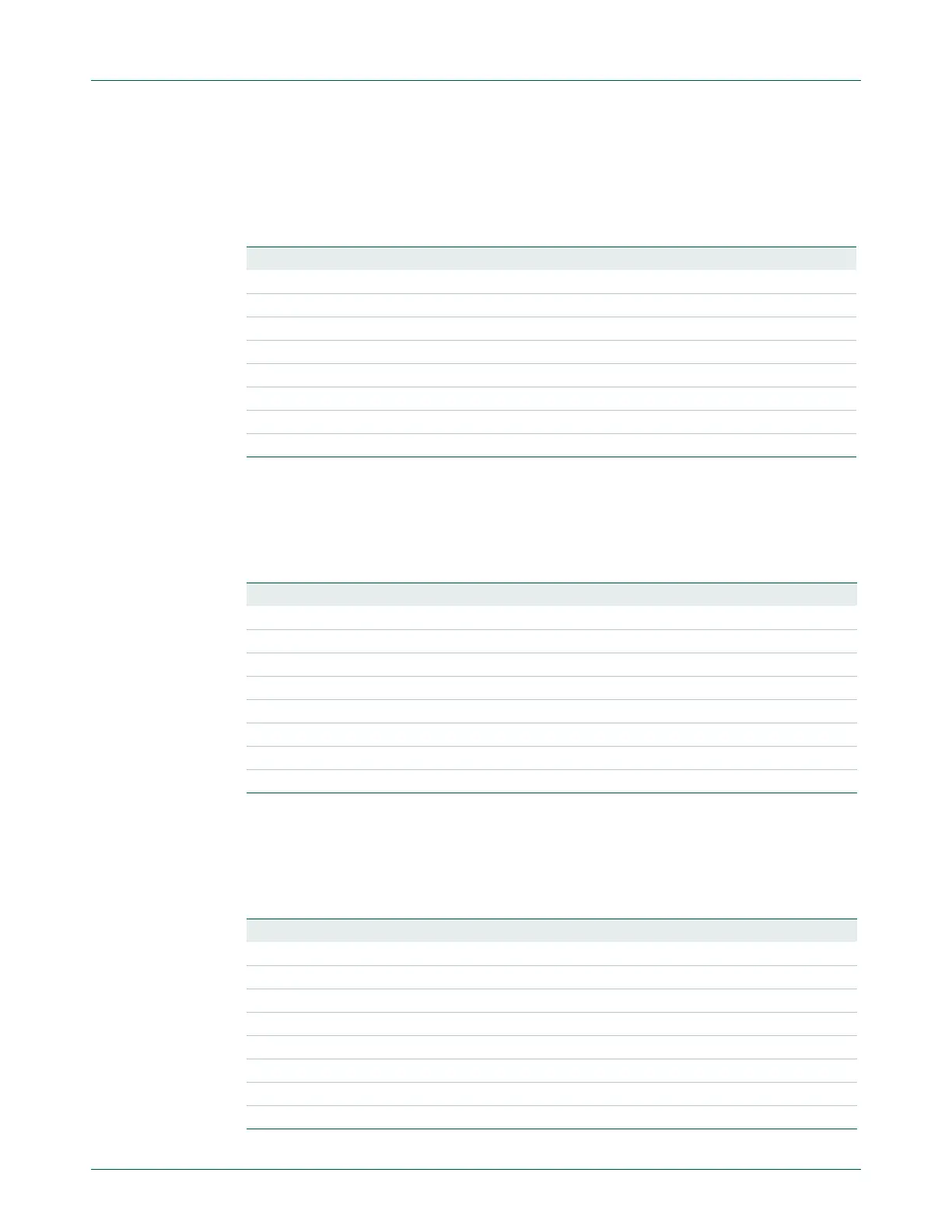

6.5.8 Interrupt Priority Register 2

The IPR2 register controls the priority of four peripheral interrupts. Each interrupt can

have one of 4 priorities, where 0 is the highest priority.

6.5.9 Interrupt Priority Register 3

The IPR3 register controls the priority of four peripheral interrupts. Each interrupt can

have one of 4 priorities, where 0 is the highest priority.

Table 67. Interrupt Priority Register 1 (IPR1, address 0xE000 E404) bit description

Bit Symbol Description Reset value

5:0 - These bits ignore writes, and read as 0. 0

7:6 IP_PIN_INT4 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

13:8 - These bits ignore writes, and read as 0. 0

15:14 IP_PIN_INT5 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

21:16 - These bits ignore writes, and read as 0. 0

23:22 IP_PIN_INT6 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

29:24 - These bits ignore writes, and read as 0. 0

31:30 IP_PIN_INT7 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

Table 68. Interrupt Priority Register 2 (IPR2, address 0xE000 E408) bit description

Bit Symbol Description Reset value

5:0 - These bits ignore writes, and read as 0. 0

7:6 IP_GINT0 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

13:8 - These bits ignore writes, and read as 0. 0

15:14 IP_GINT1 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

21:16 - These bits ignore writes, and read as 0. 0

23:22 - Reserved. 0

29:24 - These bits ignore writes, and read as 0. 0

31:30 - Reserved. 0

Table 69. Interrupt Priority Register 3 (IPR3, address 0xE000 E40C) bit description

Bit Symbol Description Reset value

5:0 - These bits ignore writes, and read as 0. 0

7:6 - Reserved. 0

13:8 - These bits ignore writes, and read as 0. 0

15:14 - Reserved. 0

21:16 - These bits ignore writes, and read as 0. 0

23:22 IP_SSP1 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

29:24 - These bits ignore writes, and read as 0. 0

31:30 IP_I2C0 Interrupt Priority. 0 = highest priority. 3 = lowest priority. 0

Loading...

Loading...