UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 386 of 523

NXP Semiconductors

UM10462

Chapter 19: LPC11U3x/2x/1x ADC

[1] Note that this does not require that the timer match function appear on a device pin.

19.5.2 A/D Global Data Register (GDR - 0x4001 C004)

The A/D Global Data Register contains the result of the most recent A/D conversion. This

includes the data, DONE, and Overrun flags, and the number of the A/D channel to which

the data relates.

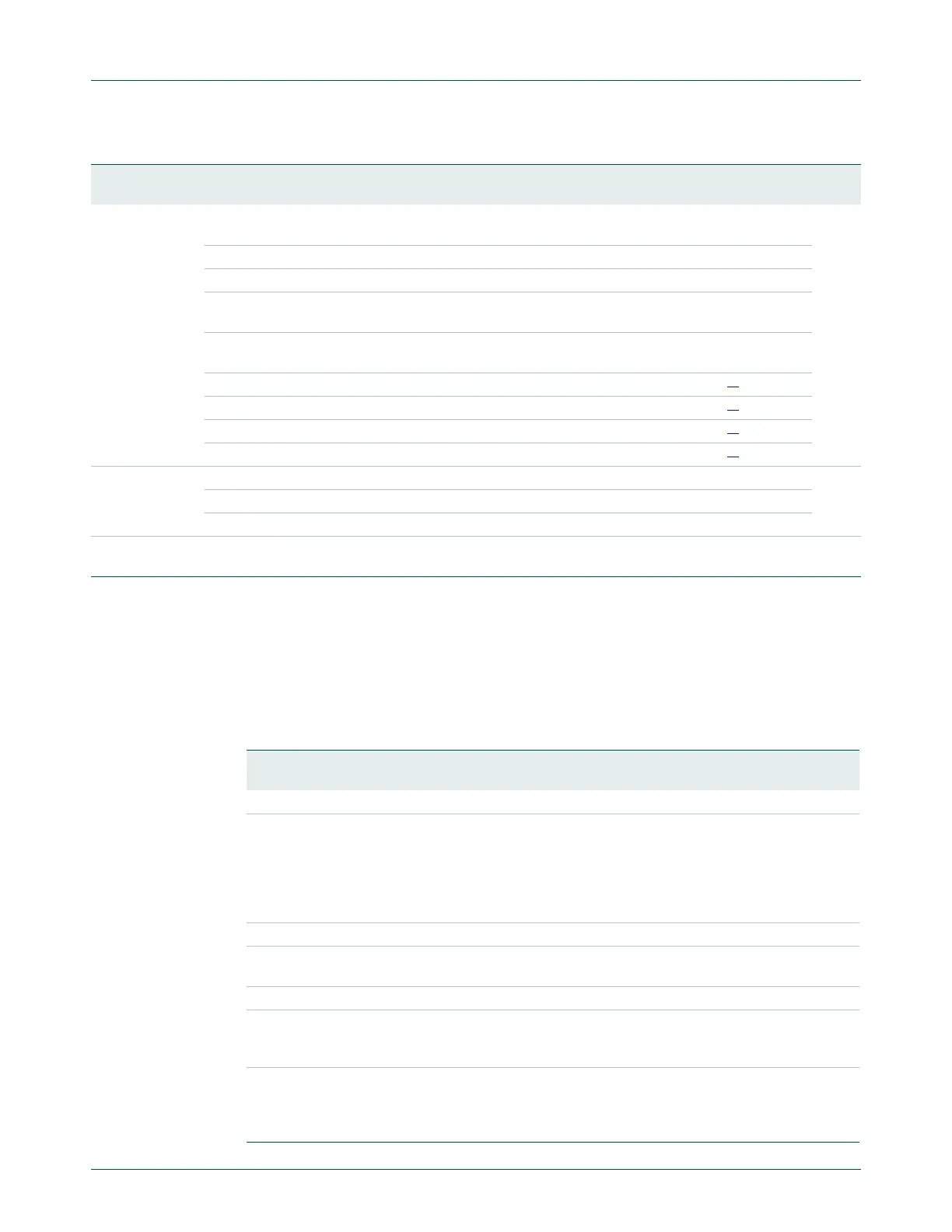

26:24 START When the BURST bit is 0, these bits control whether and when an A/D conversion is

started:

0

0x0 No start (this value should be used when clearing PDN to 0).

0x1 Start conversion now.

0x2 Start conversion when the edge selected by bit 27 occurs on a trigger signal on

CT16B0_CAP0 (independently of the pinout).

0x3 Start conversion when the edge selected by bit 27 occurs on a trigger input on

CT32B0_CAP0 (independently of the pinout).

0x4 Start conversion when the edge selected by bit 27 occurs on CT32B0_MAT0

[1]

.

0x5 Start conversion when the edge selected by bit 27 occurs on CT32B0_MAT1

[1]

.

0x6 Start conversion when the edge selected by bit 27 occurs on CT16B0_MAT0

[1]

.

0x7 Start conversion when the edge selected by bit 27 occurs on CT16B0_MAT1

[1]

.

27 EDGE This bit is significant only when the START field contains 010-111. In these cases: 0

0 Start conversion on a rising edge on the selected CAP/MAT signal.

1 Start conversion on a falling edge on the selected CAP/MAT signal.

31:28 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Table 352. A/D Control Register (CR - address 0x4001 C000) bit description

Bit Symbol Value Description Reset

Value

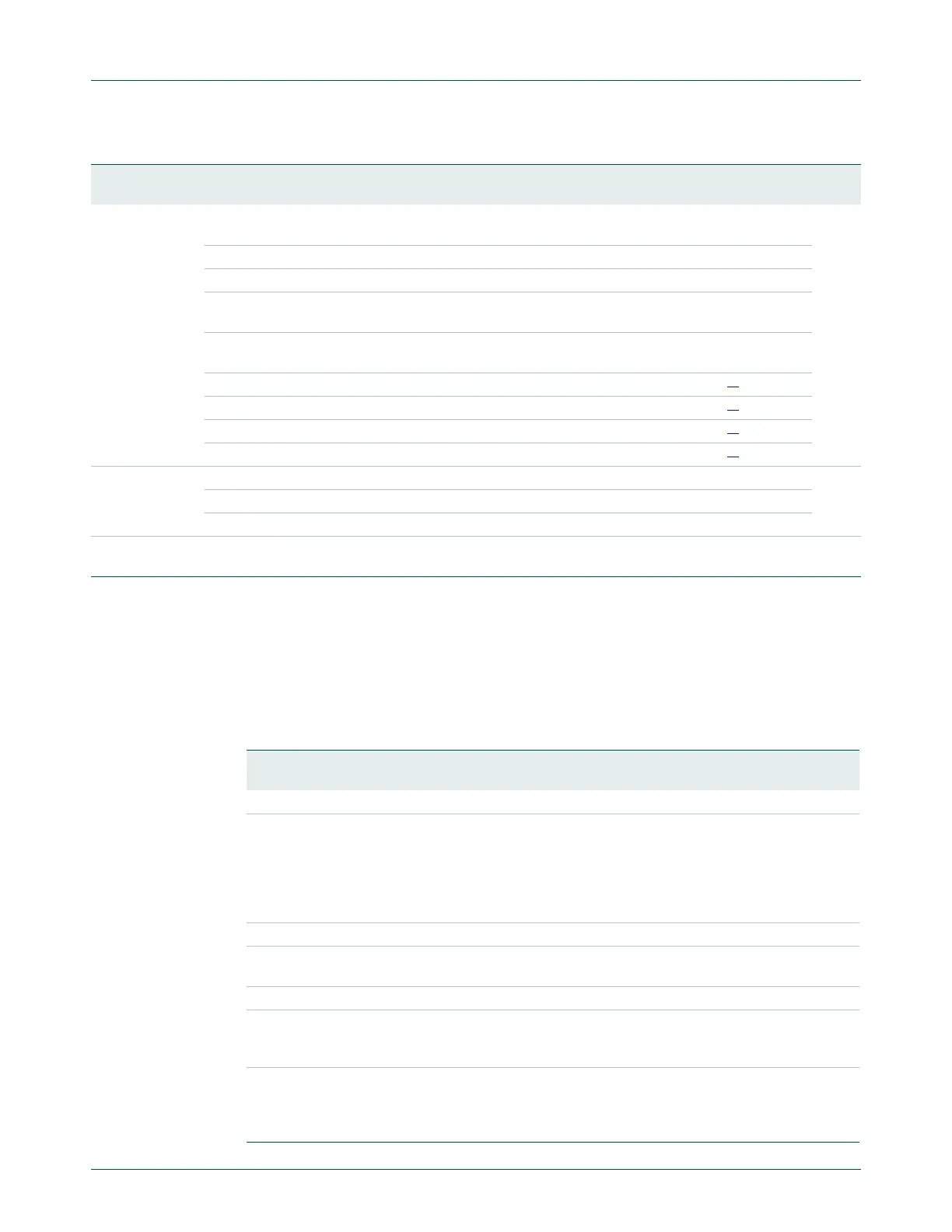

Table 353. A/D Global Data Register (GDR - address 0x4001 C004) bit description

Bit Symbol Description Reset

Value

5:0 - Reserved. These bits always read as zeros. 0

15:6 V_VREF When DONE is 1, this field contains a binary fraction representing

the voltage on the ADn pin selected by the SEL field, divided by

the voltage on the V

DD

pin. Zero in the field indicates that the

voltage on the ADn pin was less than, equal to, or close to that on

V

SS

, while 0x3FF indicates that the voltage on ADn was close to,

equal to, or greater than that on V

REF

.

X

23:16 - Reserved. These bits always read as zeros. 0

26:24 CHN These bits contain the channel from which the result bits V_VREF

were converted.

X

29:27 - Reserved. These bits always read as zeros. 0

30 OVERRUN This bit is 1 in burst mode if the results of one or more conversions

was (were) lost and overwritten before the conversion that

produced the result in the V_VREF bits.

0

31 DONE This bit is set to 1 when an A/D conversion completes. It is cleared

when this register is read and when the ADCR is written. If the

ADCR is written while a conversion is still in progress, this bit is

set and a new conversion is started.

0

Loading...

Loading...