UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 57 of 523

NXP Semiconductors

UM10462

Chapter 4: LPC11U3x/2x/1x Power Management Unit (PMU)

4.3.2 General purpose registers 0 to 3

The general purpose registers retain data through the Deep power-down mode when

power is still applied to the V

DD

pin but the chip has entered Deep power-down mode.

Only a “cold” boot when all power has been completely removed from the chip will reset

the general purpose registers.

4.3.3 General purpose register 4

The general purpose register 4 retains data through the Deep power-down mode when

power is still applied to the V

DD

pin but the chip has entered Deep power-down mode.

Only a “cold” boot, when all power has been completely removed from the chip, will reset

the general purpose registers.

Remark: If there is a possibility that the external voltage applied on pin V

DD

drops below

2.2 V during Deep power-down, the hysteresis of the WAKEUP input pin has to be

disabled in this register before entering Deep power-down mode in order for the chip to

wake up.

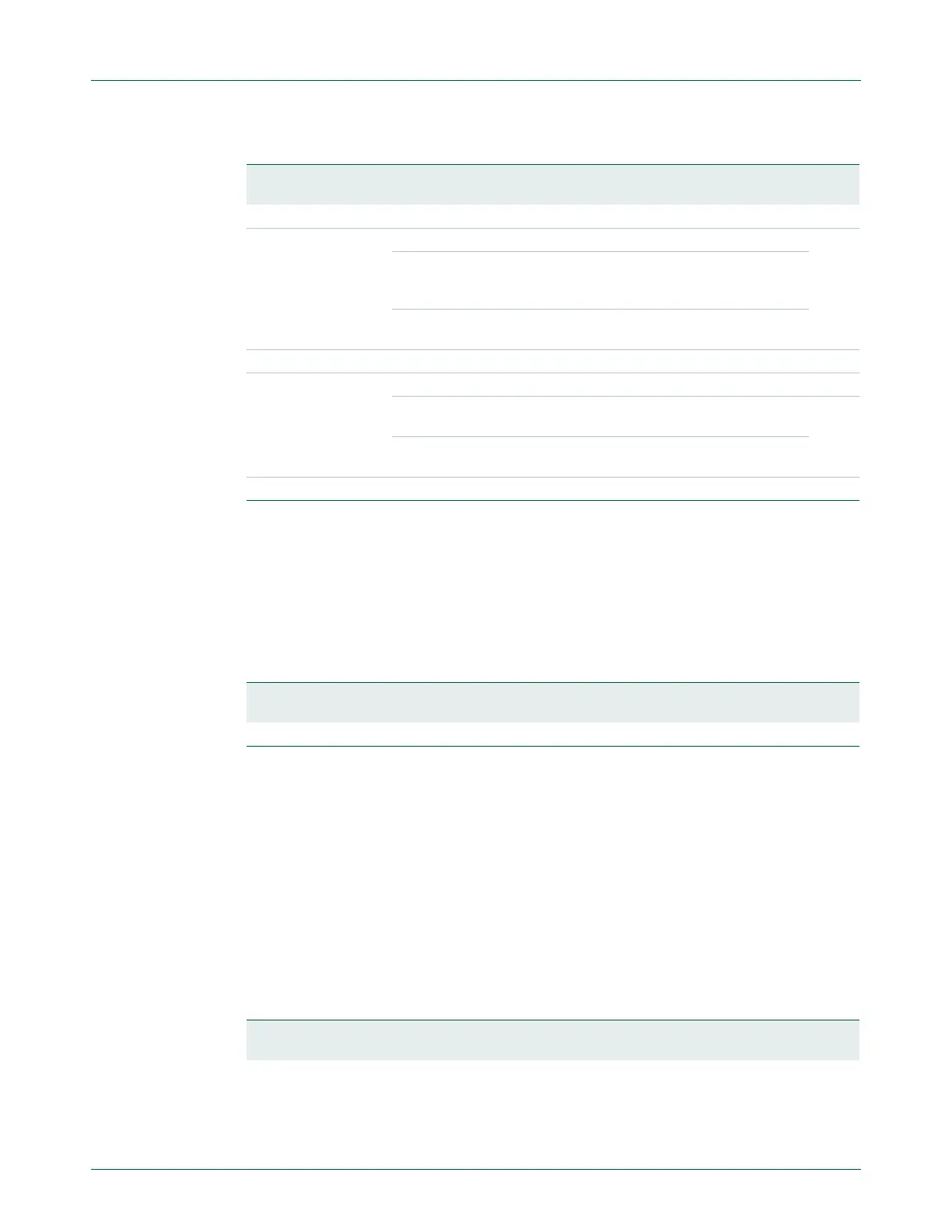

7:4 - - Reserved. Do not write ones to this bit. 0

8 SLEEPFLAG Sleep mode flag 0

0 Read: No power-down mode entered. LPC11U3x/2x/1x is

in Active mode.

Write: No effect.

1 Read: Sleep/Deep-sleep or Power-down mode entered.

Write: Writing a 1 clears the SLEEPFLAG bit to 0.

10:9 - - Reserved. Do not write ones to this bit. 0

11 DPDFLAG Deep power-down flag 0

0 Read: Deep power-down mode not entered.

Write: No effect.

0

1 Read: Deep power-down mode entered.

Write: Clear the Deep power-down flag.

31:12 - - Reserved. Do not write ones to this bit. 0

Table 54. Power control register (PCON, address 0x4003 8000) bit description

…continued

Bit Symbol Value Description Reset

value

Table 55. General purpose registers 0 to 3 (GPREG[0:3], address 0x4003 8004 (GPREG0) to

0x4003 8010 (GPREG3)) bit description

Bit Symbol Description Reset

value

31:0 GPDATA Data retained during Deep power-down mode. 0x0

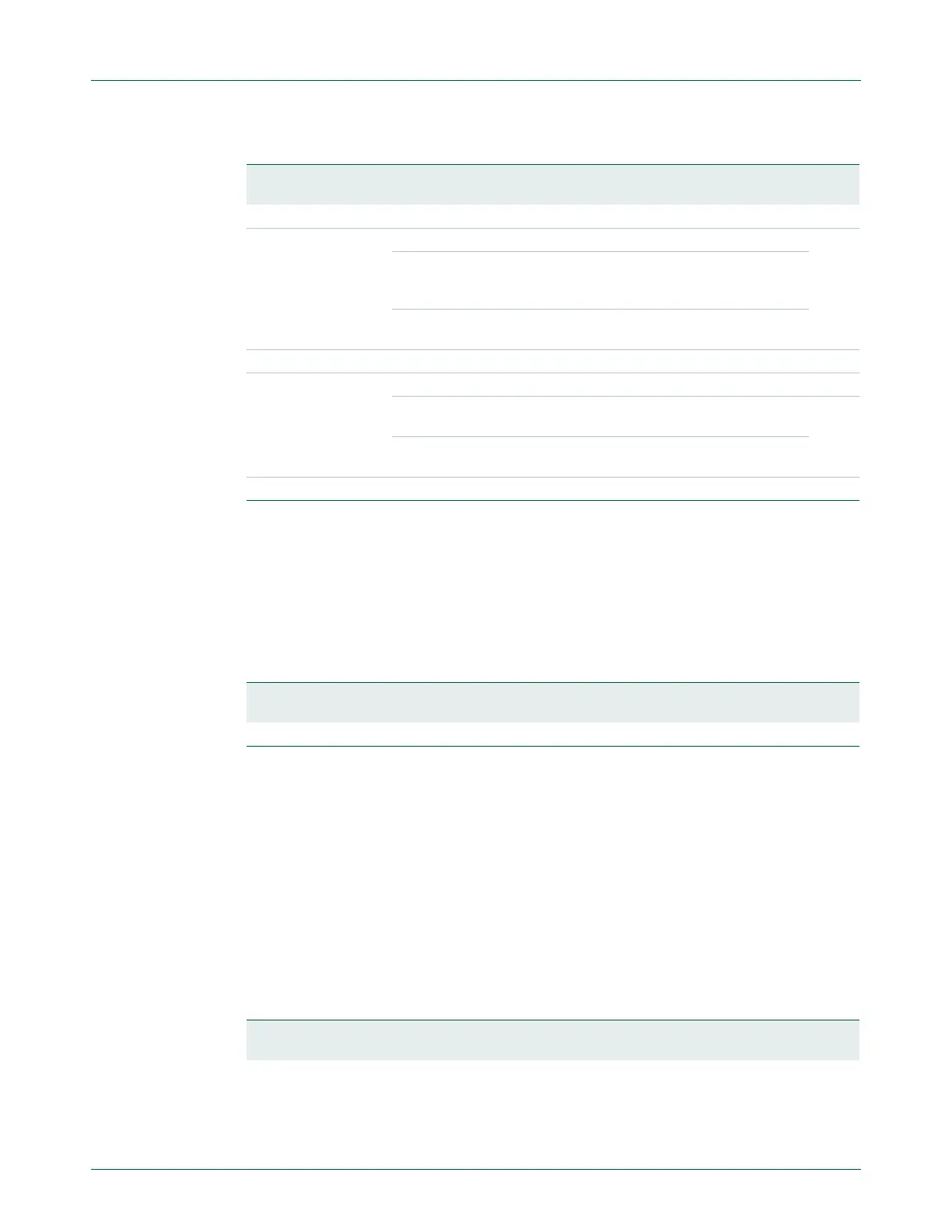

Table 56. General purpose register 4 (GPREG4, address 0x4003 8014) bit

description

Bit Symbol Value Description Reset

value

9:0 - - Reserved. Do not write ones to this bit. 0x0

Loading...

Loading...