UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 388 of 523

NXP Semiconductors

UM10462

Chapter 19: LPC11U3x/2x/1x ADC

19.6 Operation

19.6.1 Hardware-triggered conversion

If the BURST bit in the ADCR0 is 0 and the START field contains 010-111, the A/D

converter will start a conversion when a transition occurs on a selected pin or timer match

signal.

19.6.2 Interrupts

An interrupt is requested to the interrupt controller when the ADINT bit in the ADSTAT

register is 1. The ADINT bit is one when any of the DONE bits of A/D channels that are

enabled for interrupts (via the ADINTEN register) are one. Software can use the Interrupt

Enable bit in the interrupt controller that corresponds to the ADC to control whether this

results in an interrupt. The result register for an A/D channel that is generating an interrupt

must be read in order to clear the corresponding DONE flag.

19.6.3 Accuracy vs. digital receiver

While the A/D converter can be used to measure the voltage on any ADC input pin,

regardless of the pin’s setting in the IOCON block, selecting the ADC in the IOCON

registers function improves the conversion accuracy by disabling the pin’s digital receiver

(see also Section 7.3.7

).

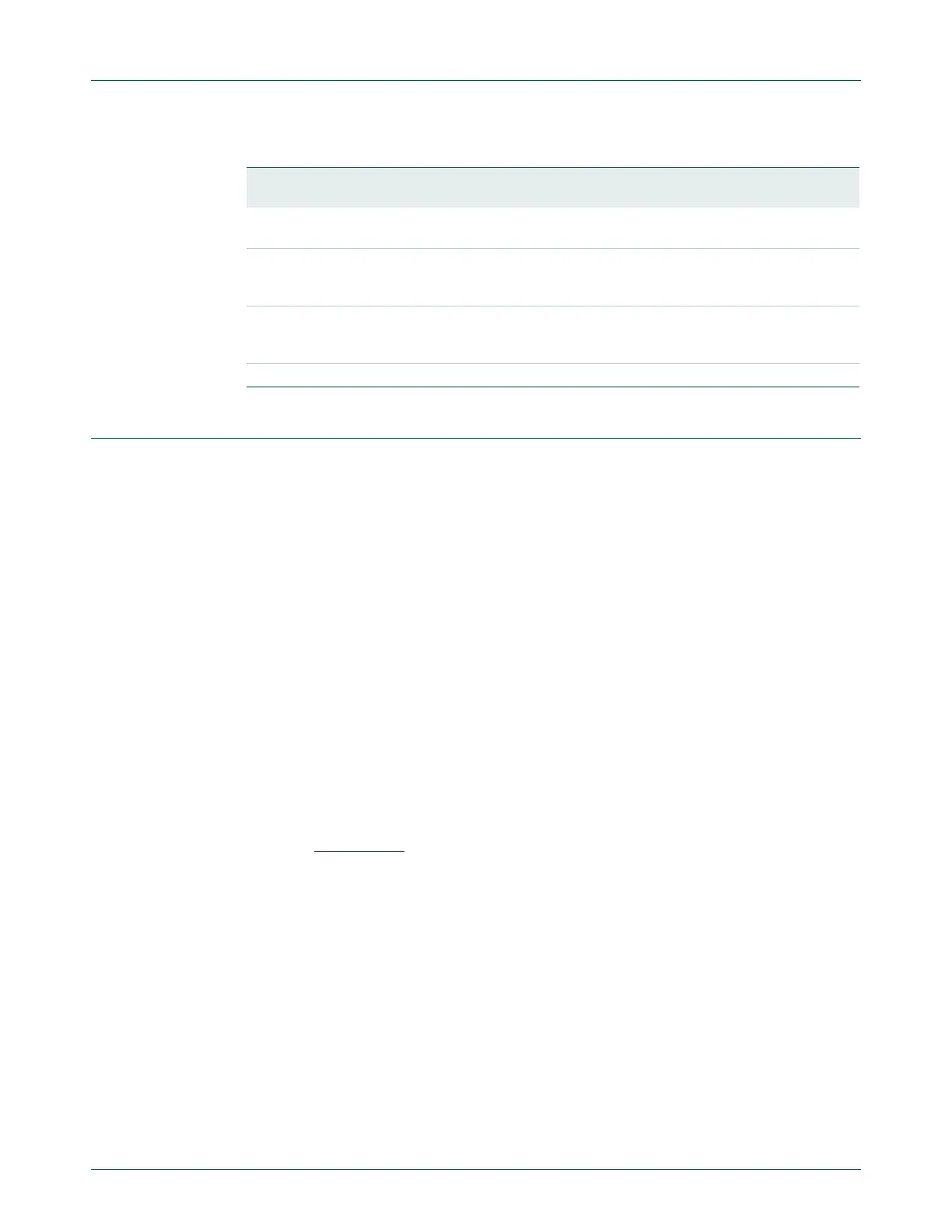

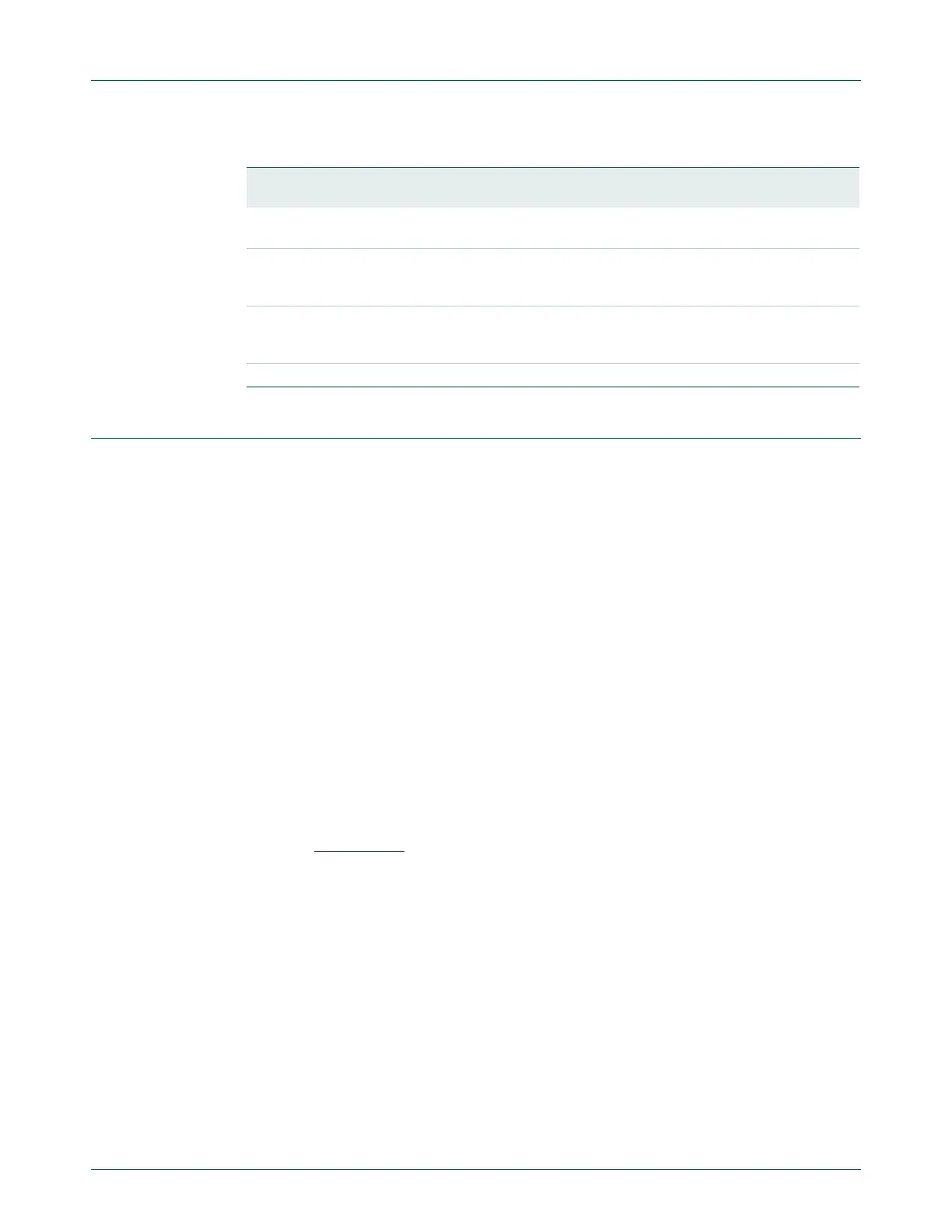

Table 356. A/D Status Register (STAT - address 0x4001 C030) bit description

Bit Symbol Description Reset

Value

7:0 DONE These bits mirror the DONE status flags that appear in the result

register for each A/D channel n.

0

15:8 OVERRUN These bits mirror the OVERRRUN status flags that appear in the

result register for each A/D channel n. Reading ADSTAT allows

checking the status of all A/D channels simultaneously.

0

16 ADINT This bit is the A/D interrupt flag. It is one when any of the

individual A/D channel Done flags is asserted and enabled to

contribute to the A/D interrupt via the ADINTEN register.

0

31:17 - Reserved. Unused, always 0. 0

Loading...

Loading...