UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 45 of 523

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

3.5.43 Flash memory access

Depending on the system clock frequency, access to the flash memory can be configured

with various access times by writing to the FLASHCFG register at address 0x4003 C010.

This register is part of the flash configuration block (see Figure 4

).

Remark: Improper setting of this register may result in incorrect operation of the

LPC11U3x/2x/1x.

3.6 Reset

Reset has the following sources on the LPC11U3x/2x/1x: the RESET pin, Watchdog

Reset, Power-On Reset (POR), and Brown Out Detect (BOD). In addition, there is an

ARM software reset.

The RESET

pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once

the operating voltage attains a usable level, starts the IRC causing reset to remain

asserted until the external Reset is de-asserted, the oscillator is running, and the flash

controller has completed its initialization.

On the assertion of any reset source (Arm software reset, POR, BOD reset, External

reset, and Watchdog reset), the following processes are initiated:

1. The IRC starts up. After the IRC-start-up time (maximum of 6 s on power-up), the

IRC provides a stable clock output.

2. The flash is powered up. This takes approximately 100 s. Then the flash initialization

sequence is started, which takes about 250 cycles.

3. The boot code in the ROM starts. The boot code performs the boot tasks and may

jump to the flash.

When the internal Reset is removed, the processor begins executing at address 0, which

is initially the Reset vector mapped from the boot block. At that point, all of the processor

and peripheral registers have been initialized to predetermined values.

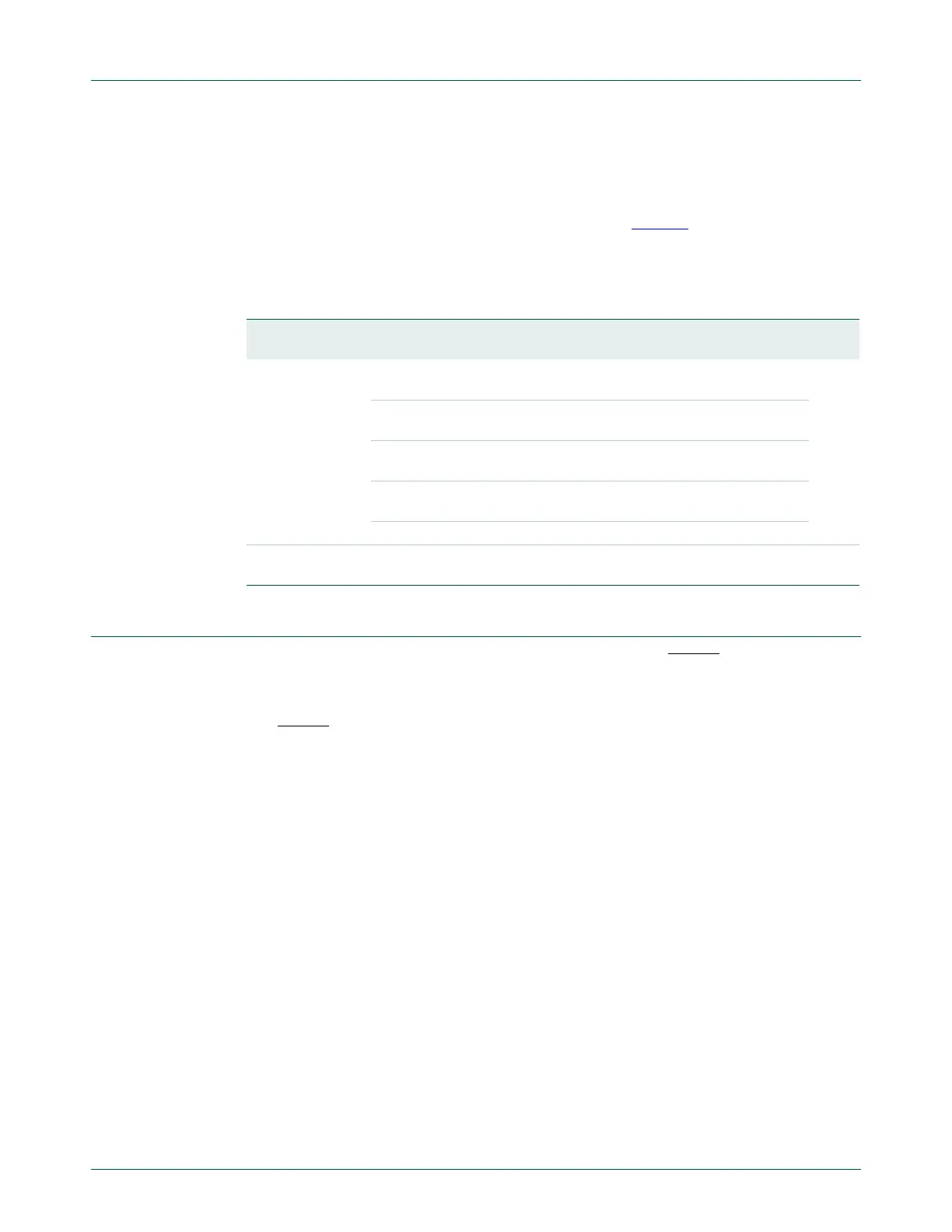

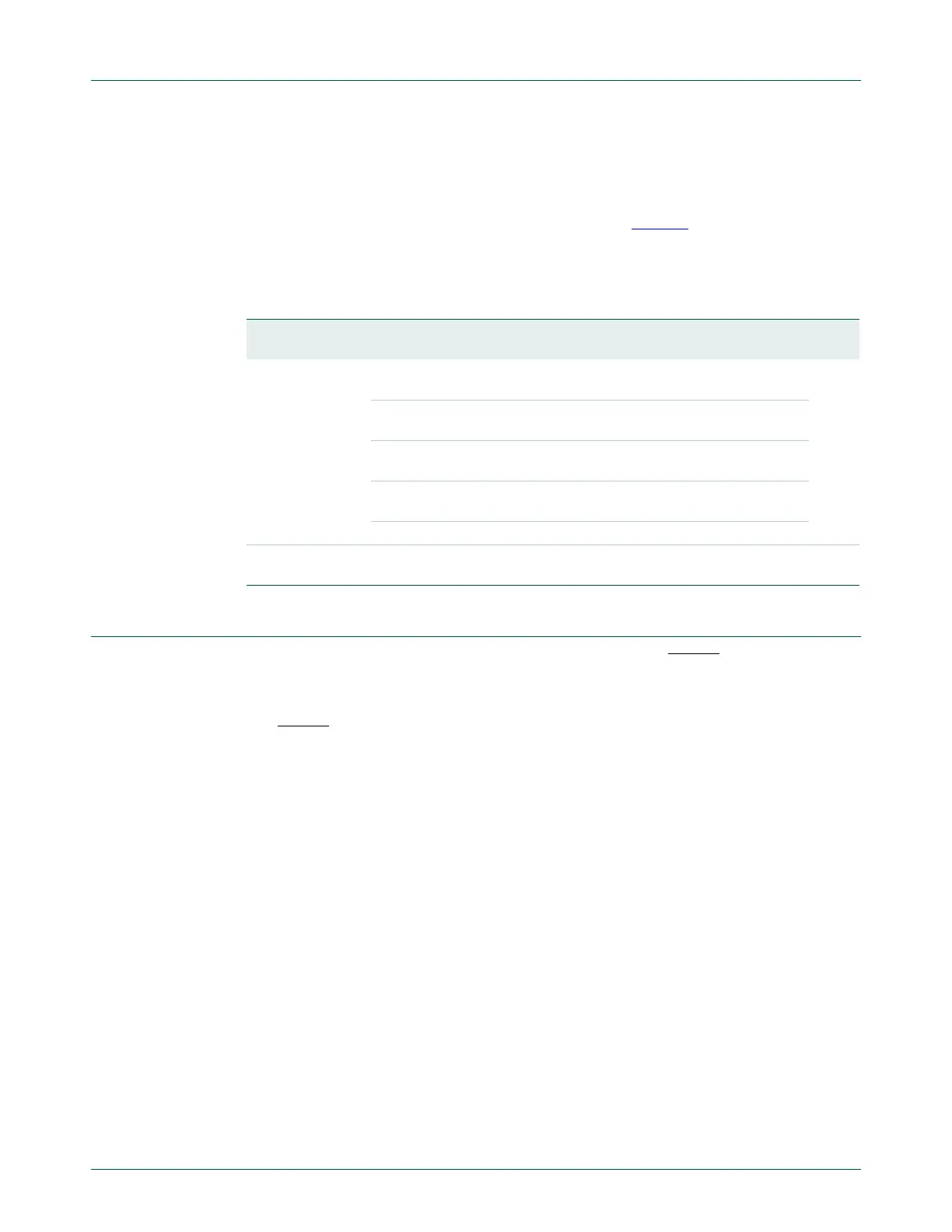

Table 49. Flash configuration register (FLASHCFG, address 0x4003 C010) bit description

Bit Symbol Value Description Reset

value

1:0 FLASHTIM Flash memory access time. FLASHTIM +1 is equal to the

number of system clocks used for flash access.

0x2

0x0 1 system clock flash access time (for system clock

frequencies of up to 20 MHz).

0x1 2 system clocks flash access time (for system clock

frequencies of up to 40 MHz).

0x2 3 system clocks flash access time (for system clock

frequencies of up to 50 MHz).

0x3 Reserved.

31:2 - - Reserved. User software must not change the value of

these bits. Bits 31:2 must be written back exactly as read.

-

Loading...

Loading...