UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 40 of 523

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

3.5.37 Interrupt wake-up enable register 0

The STARTERP0 register enables the individual GPIO pins selected through the Pin

interrupt select registers (see Table 40

) for wake-up. The pin interrupts must also be

enabled in the NVIC (interrupts 0 to 8 in Table 59

).

3.5.38 Interrupt wake-up enable register 1

This register selects which interrupts will wake the LPC11U3x/2x/1x from deep-sleep and

power-down modes. Interrupts selected by a one in these registers must be enabled in the

NVIC (Table 59

) in order to successfully wake the LPC11U3x/2x/1x from deep-sleep or

power-down mode.

The STARTERP1 register enables the WWDT interrupt, the BOD interrupt, the USB

wake-up interrupt and the two GPIO group interrupts for wake-up.

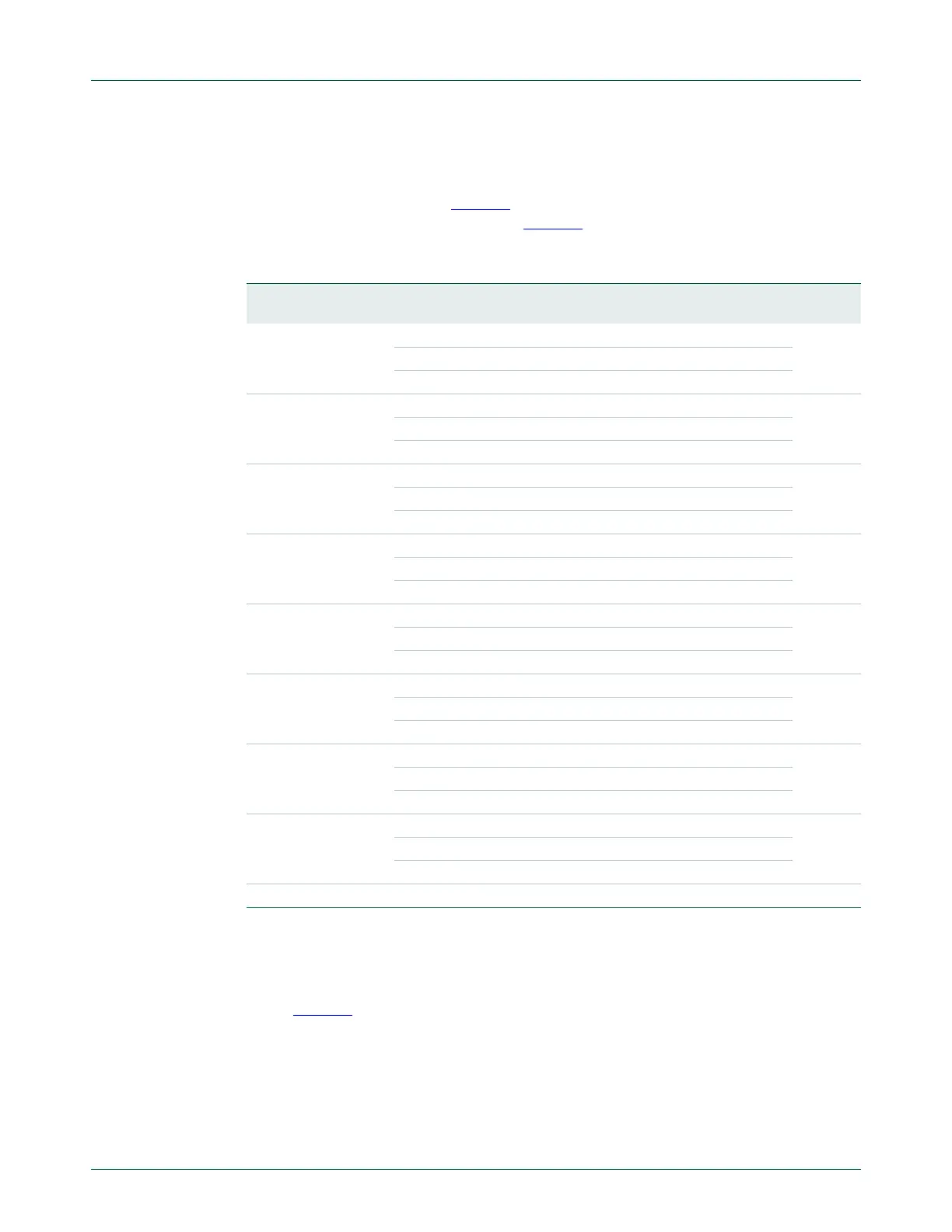

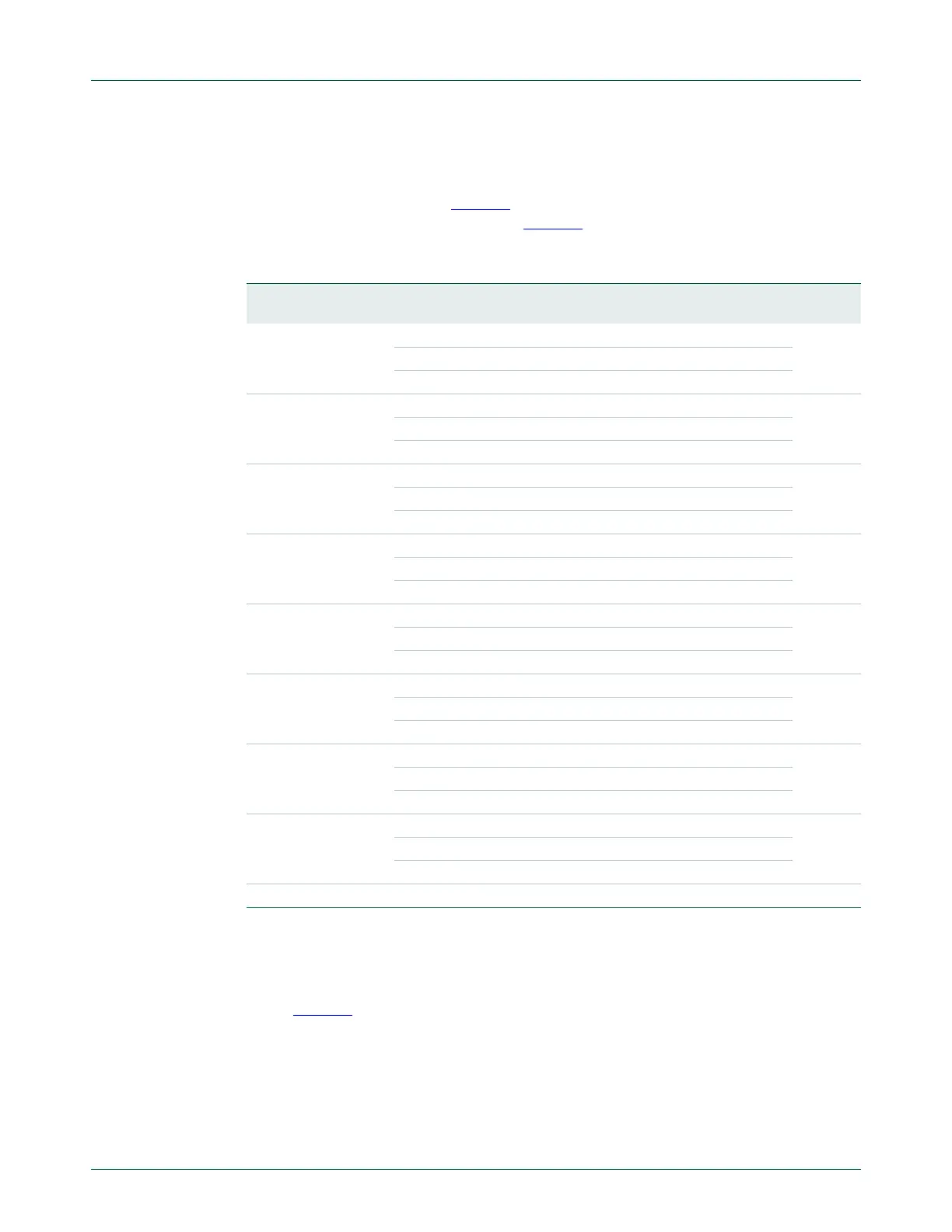

Table 43. Interrupt wake-up enable register 0 (STARTERP0, address 0x4004 8204) bit

description

Bit Symbol Value Description Reset

value

0 PINT0 Pin interrupt 0 wake-up 0

0 Disabled

1 Enabled

1 PINT1 Pin interrupt 1 wake-up 0

0 Disabled

1 Enabled

2 PINT2 Pin interrupt 2 wake-up 0

0 Disabled

1 Enabled

3 PINT3 Pin interrupt 3 wake-up 0

0 Disabled

1 Enabled

4 PINT4 Pin interrupt 4 wake-up 0

0 Disabled

1 Enabled

5 PINT5 Pin interrupt 5 wake-up 0

0 Disabled

1 Enabled

6 PINT6 Pin interrupt 6 wake-up 0

0 Disabled

1 Enabled

7 PINT7 Pin interrupt 7 wake-up 0

0 Disabled

1 Enabled

31:8 - Reserved -

Loading...

Loading...