UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 35 of 523

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

3.5.24 USB clock divider register

This register allows the USB clock usb_clk to be divided to 48 MHz. The usb_clk can be

shut down by setting the DIV bits to 0x0.

3.5.25 CLKOUT clock source select register

This register selects the signal visible on the CLKOUT pin. Any oscillator or the main clock

can be selected.

Bit 0 of the CLKOUTUEN register (see Section 3.5.26

) must be toggled from 0 to 1 for the

update to take effect.

3.5.26 CLKOUT clock source update enable register

This register updates the clock source of the CLKOUT pin with the new clock after the

CLKOUTSEL register has been written to. In order for the update to take effect at the input

of the CLKOUT pin, first write a zero to bit 0 of this register, then write a one.

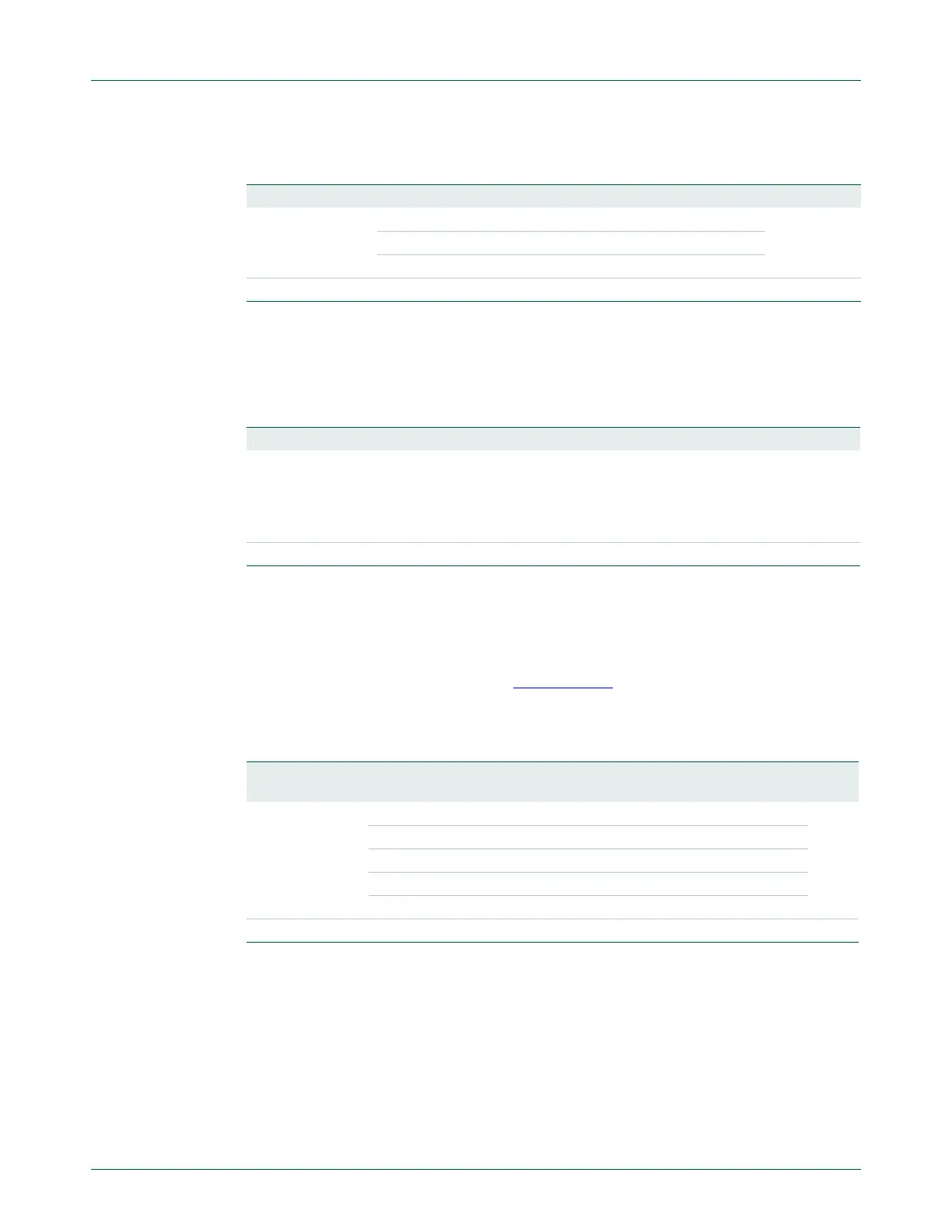

Table 29. USB clock source update enable register (USBCLKUEN, address 0x4004 80C4) bit

description

Bit Symbol Value Description Reset value

0 ENA Enable USB clock source update 0x0

0 No change

1 Update clock source

31:1 - - Reserved 0x00

Table 30. USB clock divider register (USBCLKDIV, address 0x4004 80C8) bit description

Bit Symbol Description Reset value

7:0 DIV USB clock divider values

0: Disable USB clock.

1: Divide by 1.

to

255: Divide by 255.

0x01

31:8 - Reserved 0x00

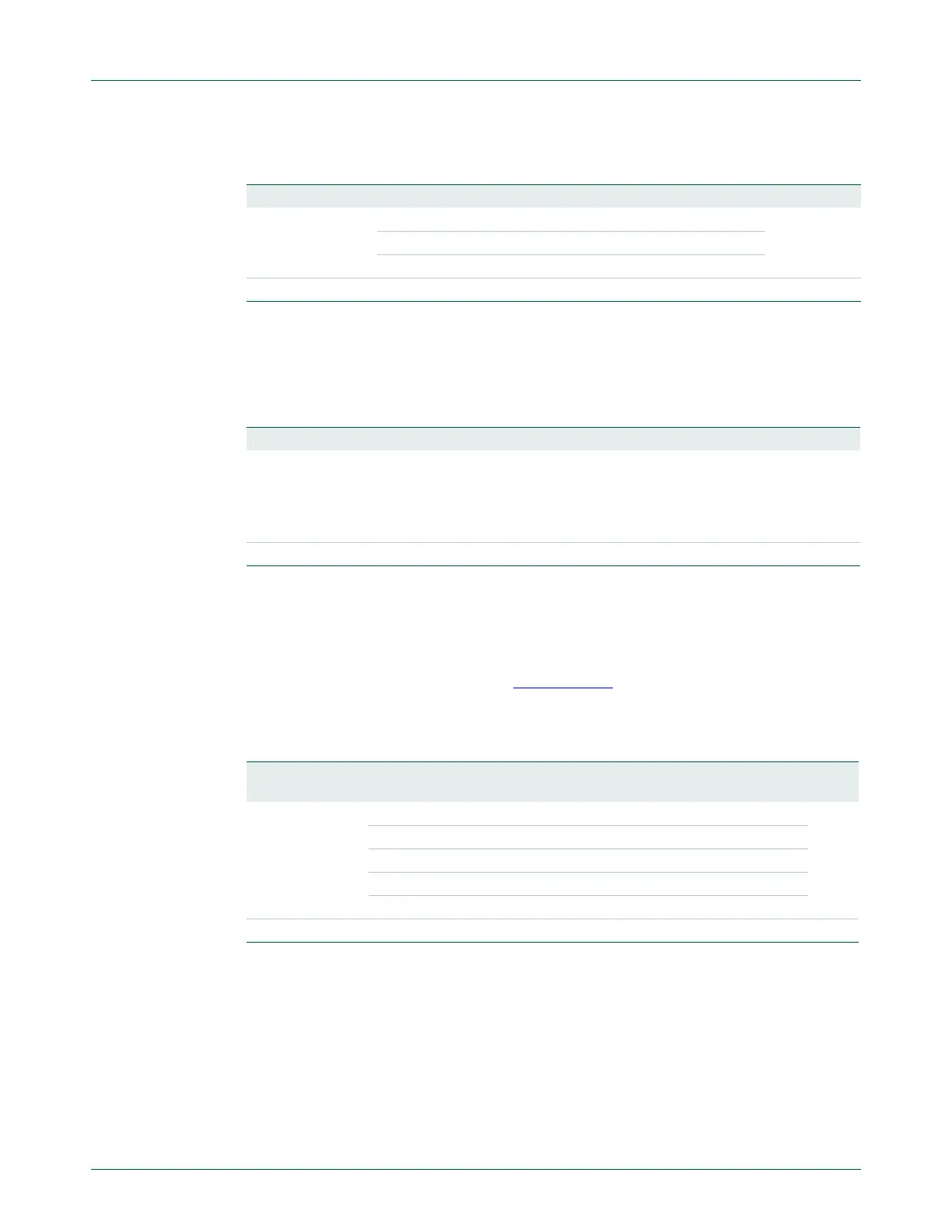

Table 31. CLKOUT clock source select register (CLKOUTSEL, address 0x4004 80E0) bit

description

Bit Symbol Value Description Reset

value

1:0 SEL CLKOUT clock source 0

0x0 IRC oscillator

0x1 Crystal oscillator (SYSOSC)

0x2 LF oscillator (watchdog oscillator)

0x3 Main clock

31:2 - - Reserved 0

Loading...

Loading...