UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 367 of 523

NXP Semiconductors

UM10462

Chapter 16: LPC11U3x/2x/1x 32-bit counter/timers CT32B0/1

16.9 Architecture

The block diagram for 32-bit counter/timer0 and 32-bit counter/timer1 is shown in

Figure 63

.

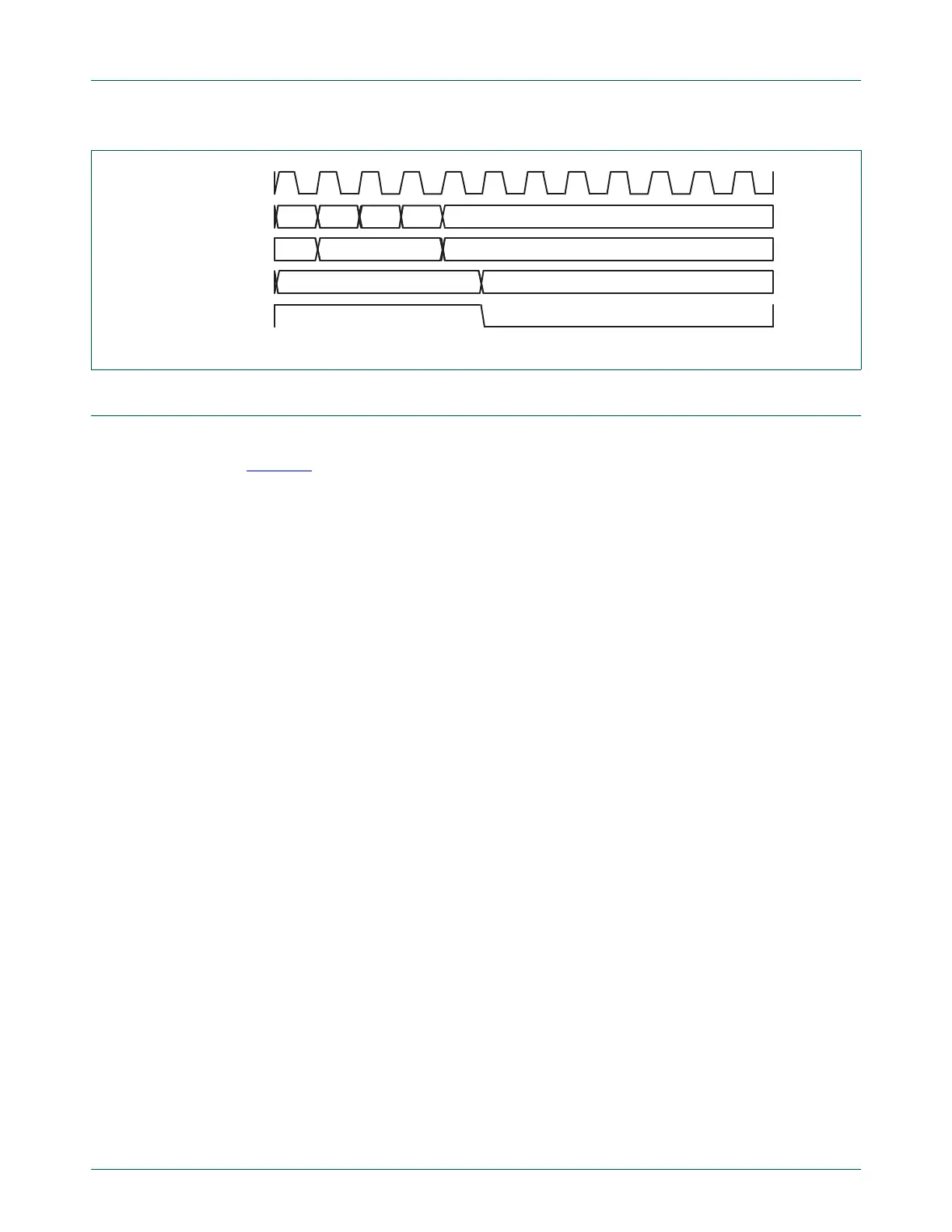

Fig 62. A timer cycle in which PR=2, MRx=6, and both interrupt and stop on match are enabled

PCLK

prescale counter

interrupt

timer counter

TCR[0]

(counter enable)

220 01

45 6

1 0

Loading...

Loading...