UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 237 of 523

NXP Semiconductors

UM10462

Chapter 11: LPC11U3x/2x/1x USB2.0 device controller

11.7.2 Control endpoint 0

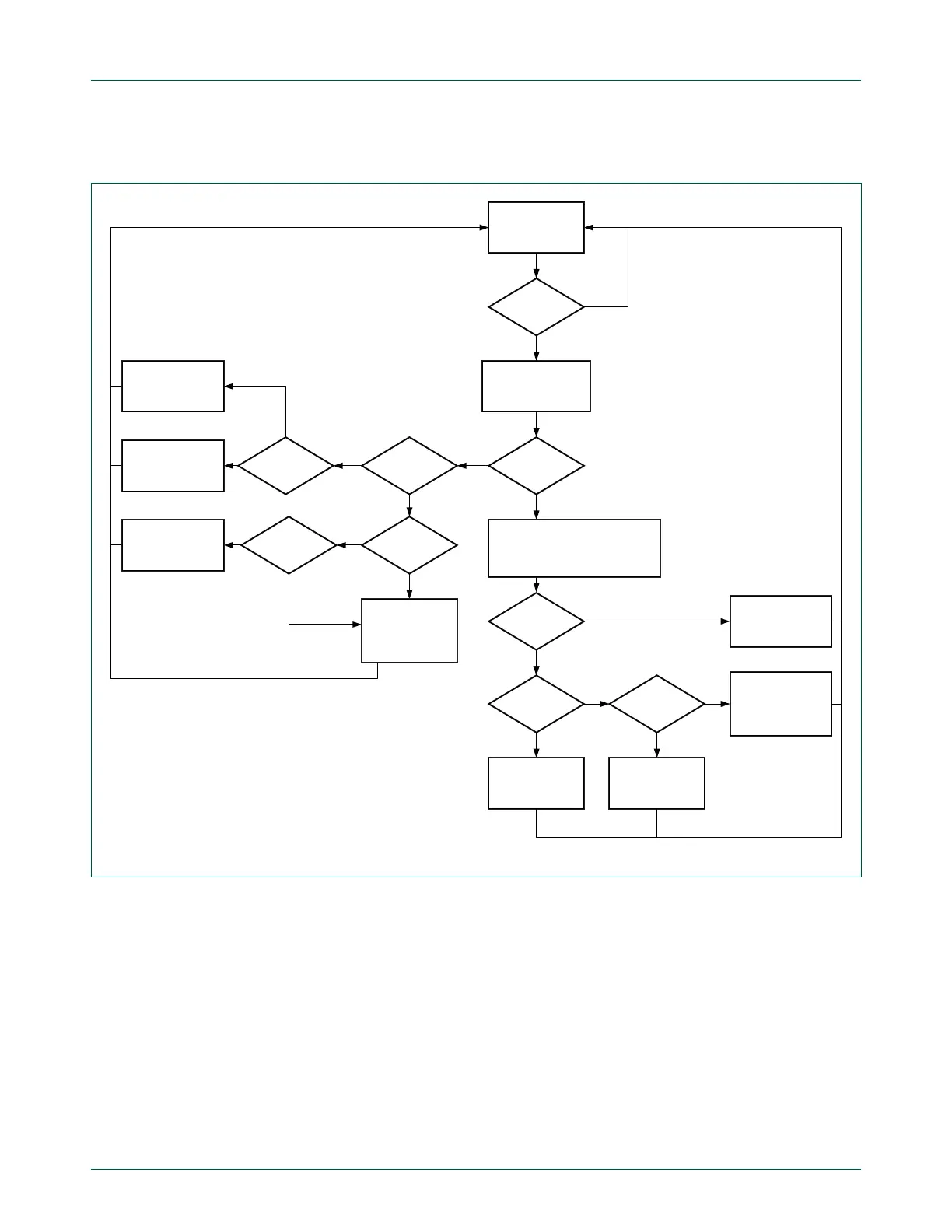

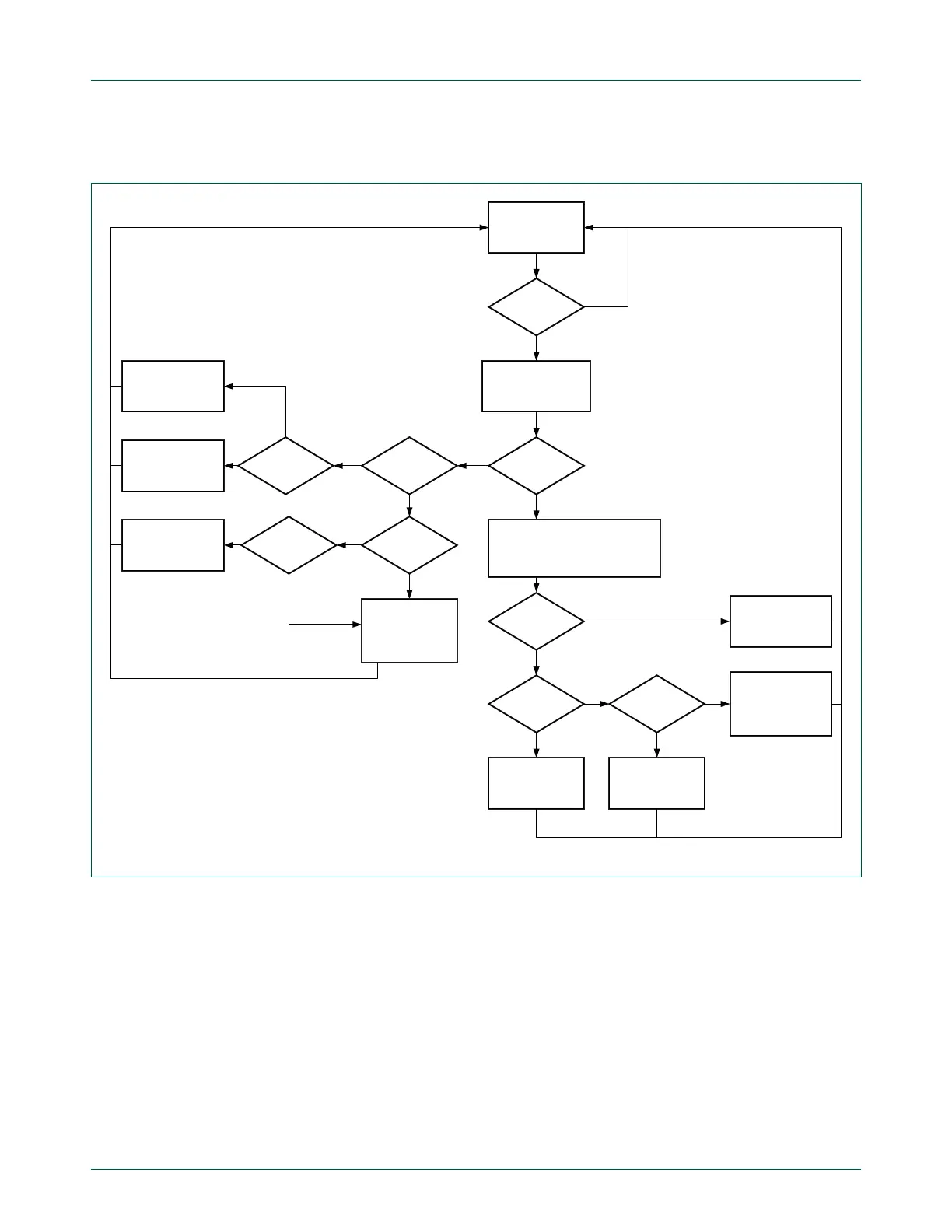

Fig 23. Flowchart of control endpoint 0 - OUT direction

Wait on EP 0Setup /Out

interrupt

EP0Setup/ Out

Interrupt = ‘1’ ?

- Clear EP0Setup /Out interrupt

- Read DevStatus (Setup ) bit

Yes

No

DevStatus(Setup ) = ‘1’ ?

Yes

- Clear EP0OUT(Active)

- Clear EP0OUT(Stall)

- Clear EP0IN(Active)

- Clear EP0IN(Stall )

- Clear EP0IN interrupt

- Clear DevStatus (Setup | IntonNak _CO | IntonNak _CI)

- Read SETUP bytes

CtrlRead ?

Yes

- Write EP0IN( Active = ‘1’

Stall = ‘1’*

NBytes)

- Write DevStatus (

IntOnNak _CO = ‘1’

IntOnNak _CI = ‘0’)

CtrlWriteNoDataStage ?

Yes

-Write EP0OUT(

Active = ‘0’

Stall = ‘1’)

- Write EP0IN( Active = ‘1’

Stall = ‘1

0 Bytes )

No

-Write EP0OUT(

Active = ‘1’

Stall = ‘1’*

NBytes)

- Write DevStatus (

IntOnNak _CO = ‘0’

IntOnNak _CI = ‘1’)

No

All OUT data received ?

- Write EP0OUT(Active = ‘1’

Stall = ‘1’*

NBytes)

No

No

Yes

- Write EP0IN( Active = ‘1’

Stall = ‘1’

0 Bytes )

- Write EP0Out (

Active = ‘0’

Stall = ‘1’)

-Clear EP0IN interrupt

SETUP request

supported ?

Yes

- Write EP0IN( Active = ‘0’

Stall = ‘1’)

-Write EP0OUT(

Active = ‘0’

Stall = ‘1’)

OUT Data phase

on-going ?

Yes

- Write EP0OUT(Active = ‘0’

Stall = ‘1’)

No

No

Note : It is very important that the

DevStatus(Setup) is only cleared after

setting EP0OUT(Active), EP0OUT(Stall),

EP0IN(Active) and EP0IN(Stall) bits are set

to zero

IN Data phase

on-going ?

EP0In Interrupt ?

No

No

Host aborts Control Write

Yes

- Write EP0OUT(Active = ‘1’

Stall = ‘1’

0 Bytes )

- Write EP0IN( Active = ‘0’

Stall = ‘1’)

- Clear EP0IN interrupt

Yes

If not all IN data transferred , the

host aborts Control Read .

Otherwise it is a normal completion

by the host

* : STALL bit must only be set when it is the last packet during the data phase for this Control Transfer

Loading...

Loading...