UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 94 of 523

NXP Semiconductors

UM10462

Chapter 7: LPC11U3x/2x/1x I/O configuration

7.4.1.12 TDI_PIO0_11 register

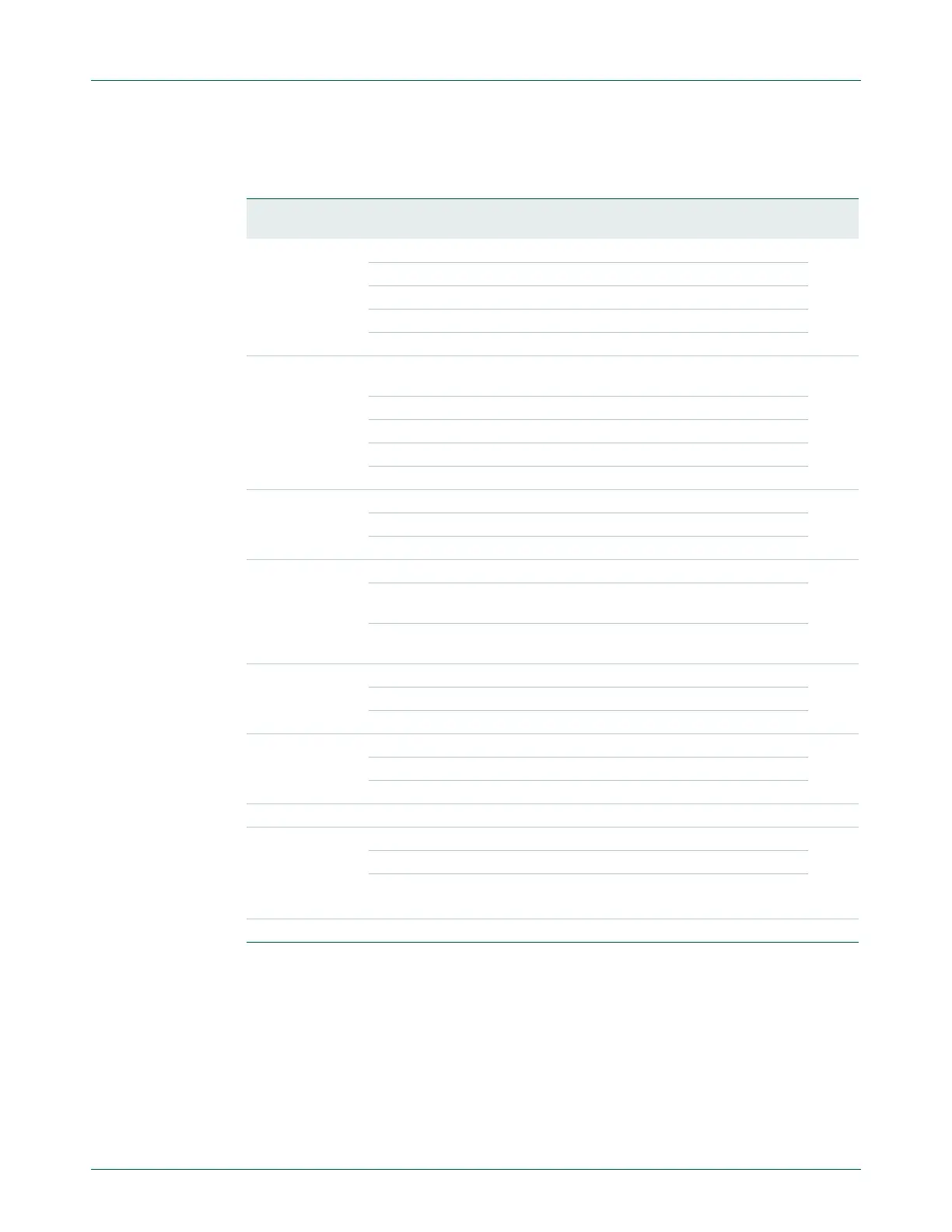

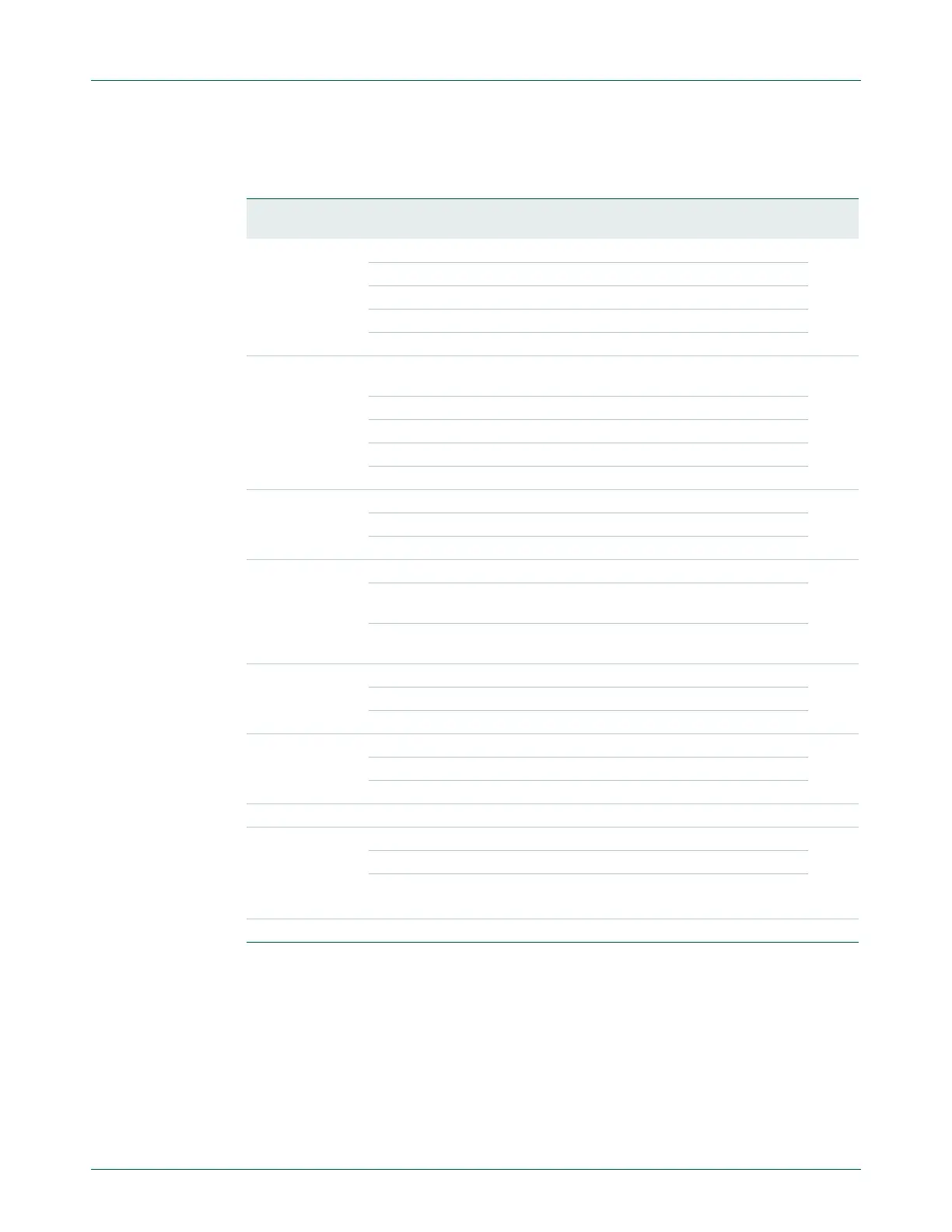

Table 87. TDI_PIO0_11 register (TDI_PIO0_11, address 0x4004 402C) bit description

Bit Symbol Value Description Reset

value

2:0 FUNC Selects pin function. Values 0x4 to 0x7 are reserved. 000

0x0 TDI.

0x1 PIO0_11.

0x2 AD0.

0x3 CT32B0_MAT3.

4:3 MODE Selects function mode (on-chip pull-up/pull-down resistor

control).

10

0x0 Inactive (no pull-down/pull-up resistor enabled).

0x1 Pull-down resistor enabled.

0x2 Pull-up resistor enabled.

0x3 Repeater mode.

5 HYS Hysteresis. 0

0 Disable.

1 Enable.

6 INV Invert input 0

0 Input not inverted (HIGH on pin reads as 1, LOW on pin reads

as 0).

1 Input inverted (HIGH on pin reads as 0, LOW on pin reads as

1).

7 ADMODE Selects Analog/Digital mode. 1

0 Analog input mode.

1 Digital functional mode.

8 FILTR Selects 10 ns input glitch filter. 0

0 Filter enabled.

1 Filter disabled.

9 - - Reserved. 0

10 OD Open-drain mode. 0

0 Disable.

1 Open-drain mode enabled.

Remark: This is not a true open-drain mode.

31:11 - - Reserved. 0

Loading...

Loading...