UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 71 of 523

NXP Semiconductors

UM10462

Chapter 6: LPC11U3x/2x/1x NVIC

6.5.1 Interrupt Set Enable Register 0 register

The ISER0 register allows to enable peripheral interrupts or to read the enabled state of

those interrupts. Disable interrupts through the ICER0 (Section 6.5.2

).

The bit description is as follows for all bits in this register:

Write — Writing 0 has no effect, writing 1 enables the interrupt.

Read — 0 indicates that the interrupt is disabled, 1 indicates that the interrupt is enabled.

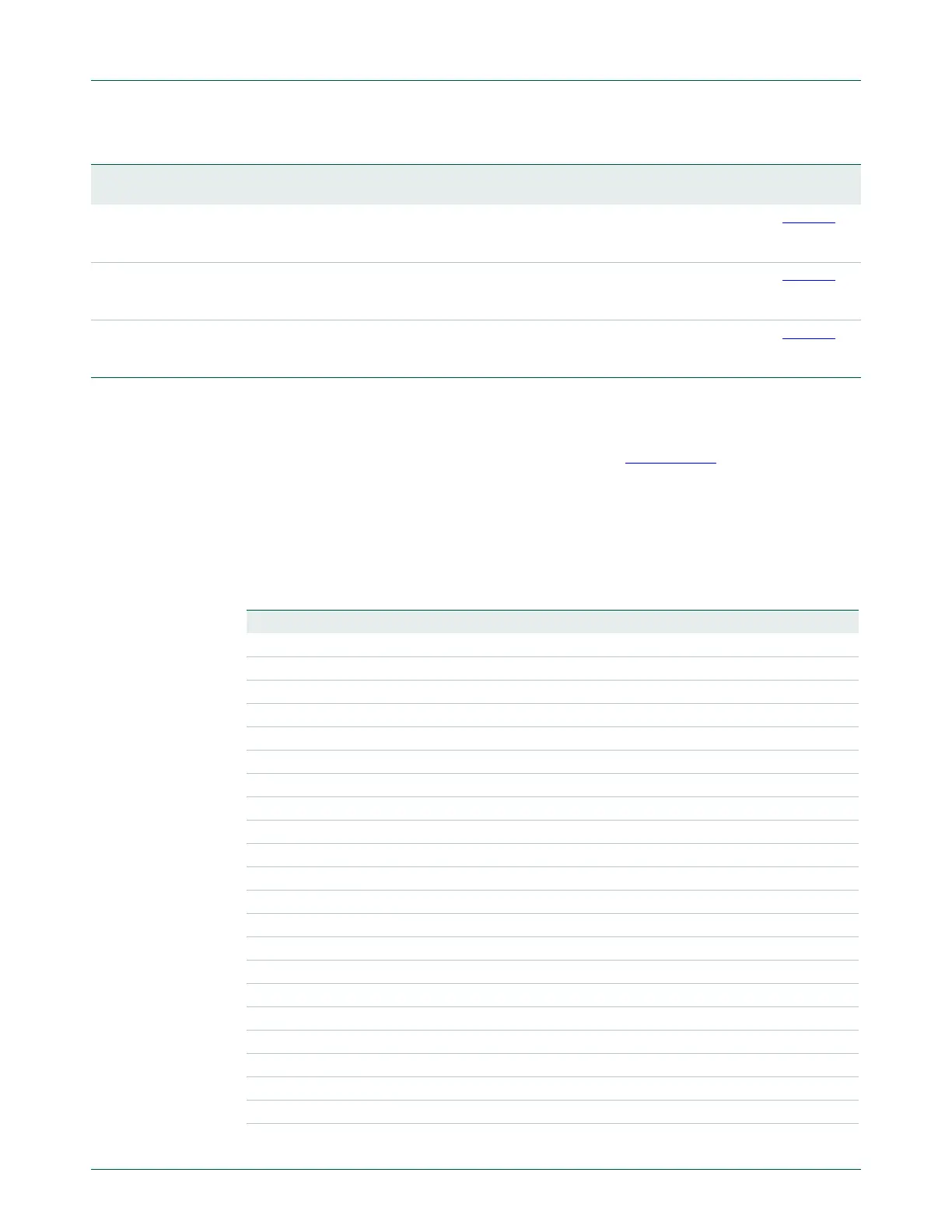

IPR5 R/W 0x414 Interrupt Priority Registers 5. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 12 to 15.

0 Table 71

IPR6 R/W 0x418 Interrupt Priority Registers 6. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 24 to 27.

0 Table 72

IPR7 R/W 0x41C Interrupt Priority Registers 7. This register allows assigning a priority

to each interrupt. This register contains the 2-bit priority fields for

interrupts 28 to 31.

0 Table 73

Table 60. Register overview: NVIC (base address 0xE000 E000) …continued

Name Access Address

offset

Description Reset

value

Reference

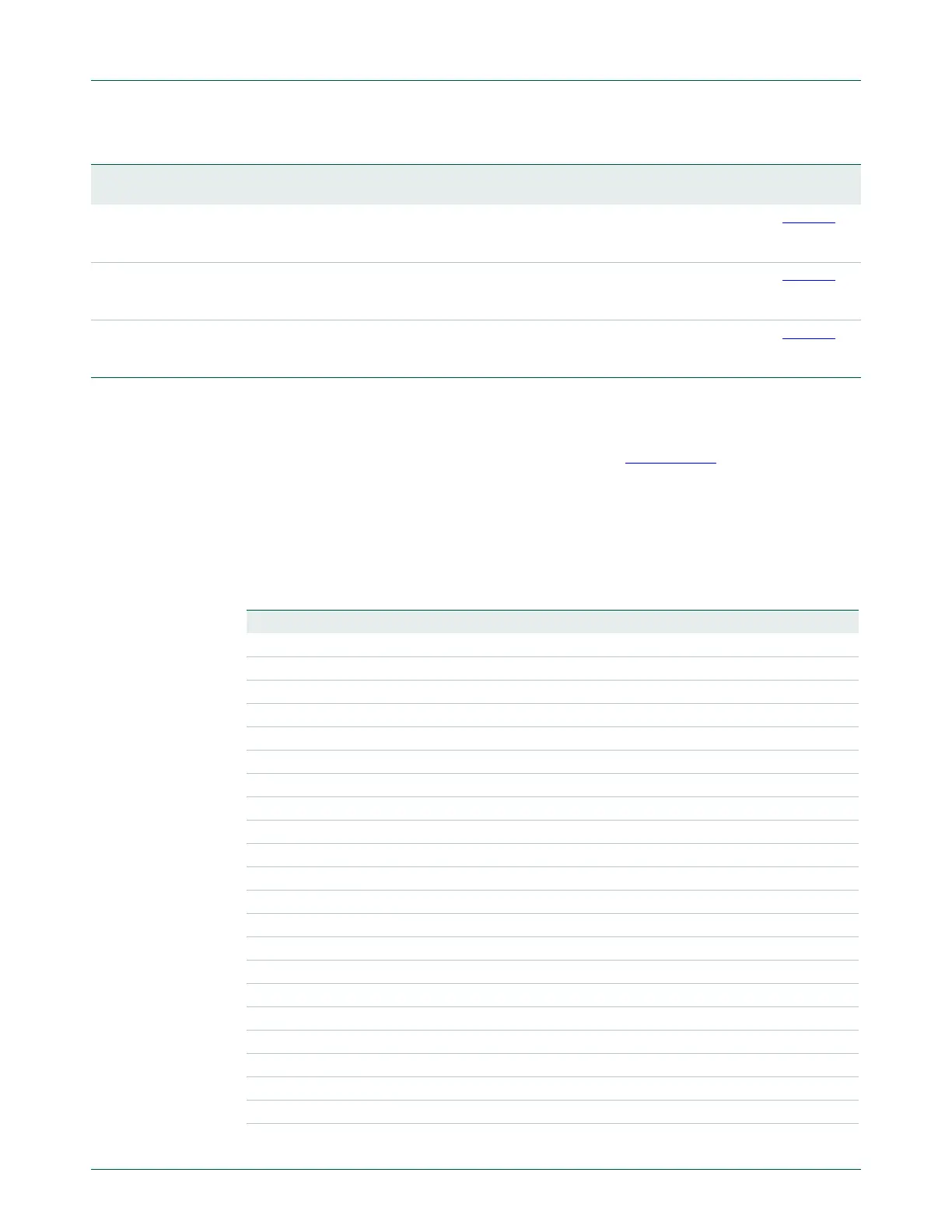

Table 61. Interrupt Set Enable Register 0 register (ISER0, address 0xE000 E100) bit

description

Bit Symbol Description Reset value

0 ISE_PININT0 Interrupt enable. 0

1 ISE_PININT1 Interrupt enable. 0

2 ISE_PININT2 Interrupt enable. 0

3 ISE_PININT3 Interrupt enable. 0

4 ISE_PININT4 Interrupt enable. 0

5 ISE_PININT5 Interrupt enable. 0

6 ISE_PININT6 Interrupt enable. 0

7 ISE_PININT7 Interrupt enable. 0

8 ISE_GINT0 Interrupt enable. 0

9 ISE_GINT1 Interrupt enable. 0

10 - Reserved. 0

11 - Reserved. 0

12 - Reserved. 0

13 - Reserved. 0

14 ISE_SSP1 Interrupt enable. 0

15 ISE_I2C0 Interrupt enable. 0

16 ISE_CT16B0 Interrupt enable. 0

17 ISE_CT16B1 Interrupt enable. 0

18 ISE_CT32B0 Interrupt enable. 0

19 ISE_CT32B1 Interrupt enable. 0

20 ISE_SSP0 Interrupt enable. 0

21 ISE_USART0 Interrupt enable. 0

Loading...

Loading...