UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 30 of 523

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

3.5.15 Main clock source select register

This register selects the main system clock, which can be the system PLL (sys_pllclkout),

or the watchdog oscillator, or the IRC oscillator. The main system clock clocks the core,

the peripherals, and the memories.

Bit 0 of the MAINCLKUEN register (see Section 3.5.16

) must be toggled from 0 to 1 for

the update to take effect.

3.5.16 Main clock source update enable register

This register updates the clock source of the main clock with the new input clock after the

MAINCLKSEL register has been written to. In order for the update to take effect, first write

a zero to bit 0 of this register, then write a one.

3.5.17 System clock divider register

This register controls how the main clock is divided to provide the system clock to the

core, memories, and the peripherals. The system clock can be shut down completely by

setting the DIV field to zero.

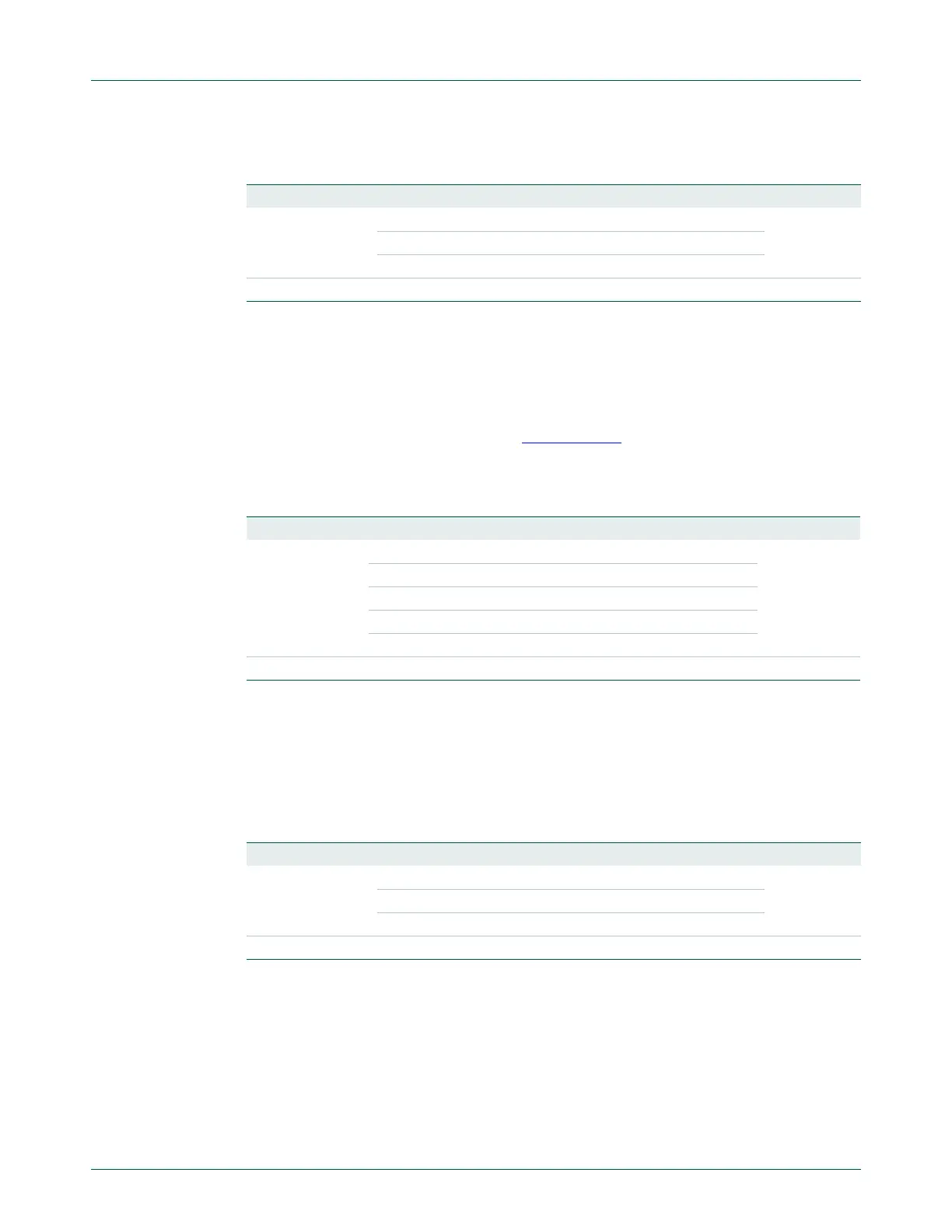

Table 20. USB PLL clock source update enable register (USBPLLCLKUEN, address 0x4004

804C) bit description

Bit Symbol Value Description Reset value

0 ENA Enable USB PLL clock source update 0x0

0 No change

1 Update clock source

31:1 - - Reserved 0x00

Table 21. Main clock source select register (MAINCLKSEL, address 0x4004 8070) bit

description

Bit Symbol Value Description Reset value

1:0 SEL Clock source for main clock 0

0x0 IRC Oscillator

0x1 PLL input

0x2 Watchdog oscillator

0x3 PLL output

31:2 - - Reserved -

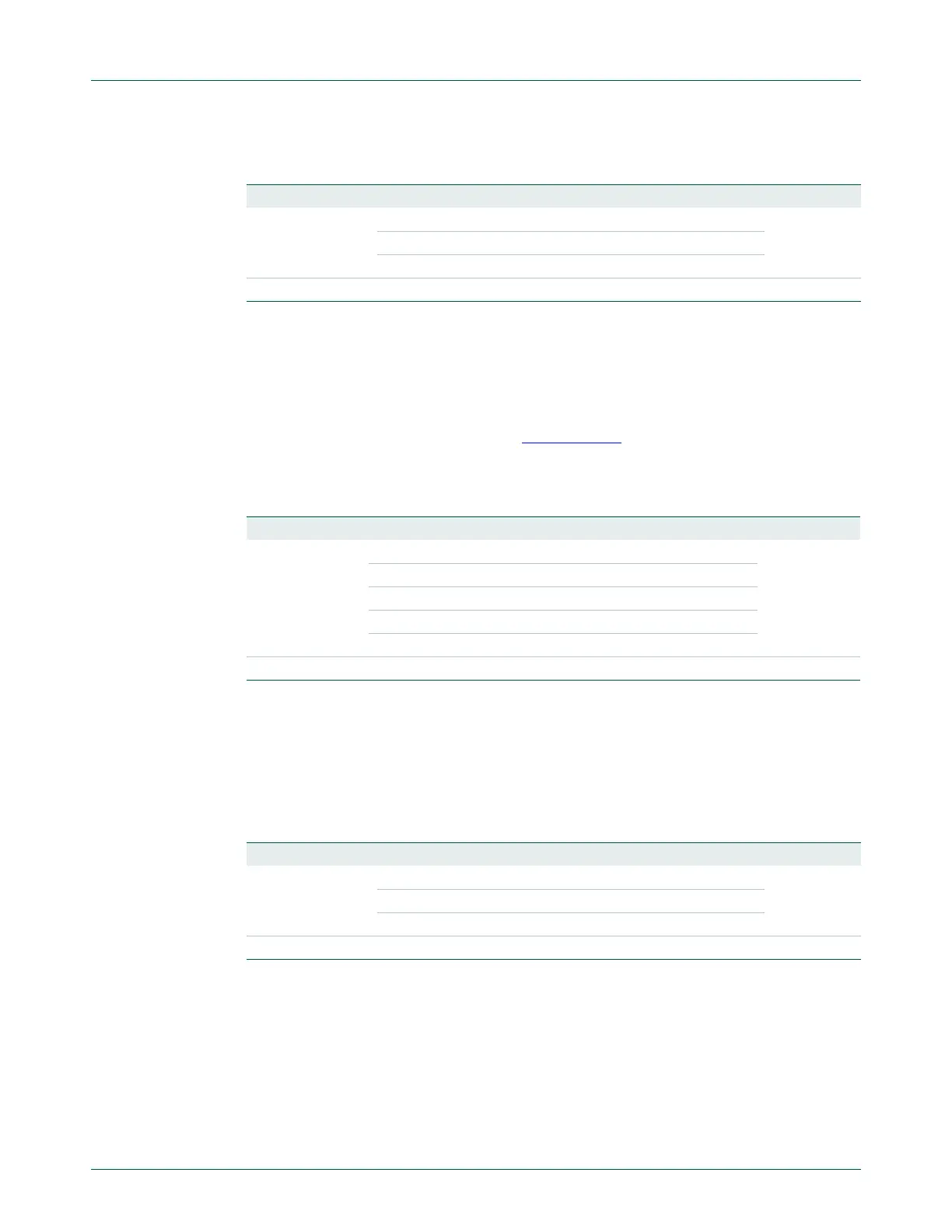

Table 22. Main clock source update enable register (MAINCLKUEN, address 0x4004 8074)

bit description

Bit Symbol Value Description Reset value

0 ENA Enable main clock source update 1

0 No change

1 Update clock source

31:1 - - Reserved -

Loading...

Loading...