R&S FSL TRACe Subsystem

1300.2519.12 6.265 E-11

TRACe:IQ Subsystem

The commands of this subsystem are used for collection and output of measured IQ data. A special

memory is therefore available in the instrument for about 512k complex samples (pairs of I and Q data).

The measurement is always performed in zero span at the selected center frequency. The number of

complex samples to be collected and the sample rate can be set (for details refer to "Sample rate and

maximum usable bandwidth" on page 6.267). Prior to being stored in memory or output via GPIB, the

measurement data are corrected in terms of frequency response.

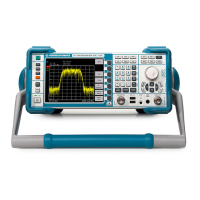

The block diagrams below show the analyzer hardware from the IF section to the processor. The block

diagrams differ between the instrument models because two different motherboards are fitted. The main

difference is the position of the fractional resampling and the analog IF bandwidth. For details on the

distinction refer to "Sample rate and maximum usable bandwidth" on page 6.267.

The A/D converter samples the IF signal (47.9 MHz) at a rate of

MHz365.8 . The digital signal is

down–converted to the complex baseband, lowpass–filtered, and the sampling rate is reduced. The

continuously adjustable sampling rates are realized using an optimal decimation filter and subsequent

resampling on the set sampling rate.

The I/Q data are written to separate memories of 512 k words each. The memories are hardware–

triggered. 512 samples are designated as buffer for triggering, which leads to a max. recording length of

523776 (=512k – 512) complex samples.

I memory

512 k

processor

analog IF

filter

bandwidth

28 MHz

analyzer IF

47.9 MHz

A

D

A/D

converter

65.83 MHz

sampling

clock

digital down conversion

+ continuous decimation

cos

sin

decimation

filters

NCO

-47.9 MHz

Q memory

512 k

arbitrary

sampling rate

10kHz ... 65.83MHz

Data aquisition hardware

I data

Q data

Trigger

fractional resampling

Fig. 6–1 Signal processing in models with UDC motherboards

Loading...

Loading...