Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 127

UG366 (v2.5) January 17, 2011

Chapter 3

Transmitter

TX Overview

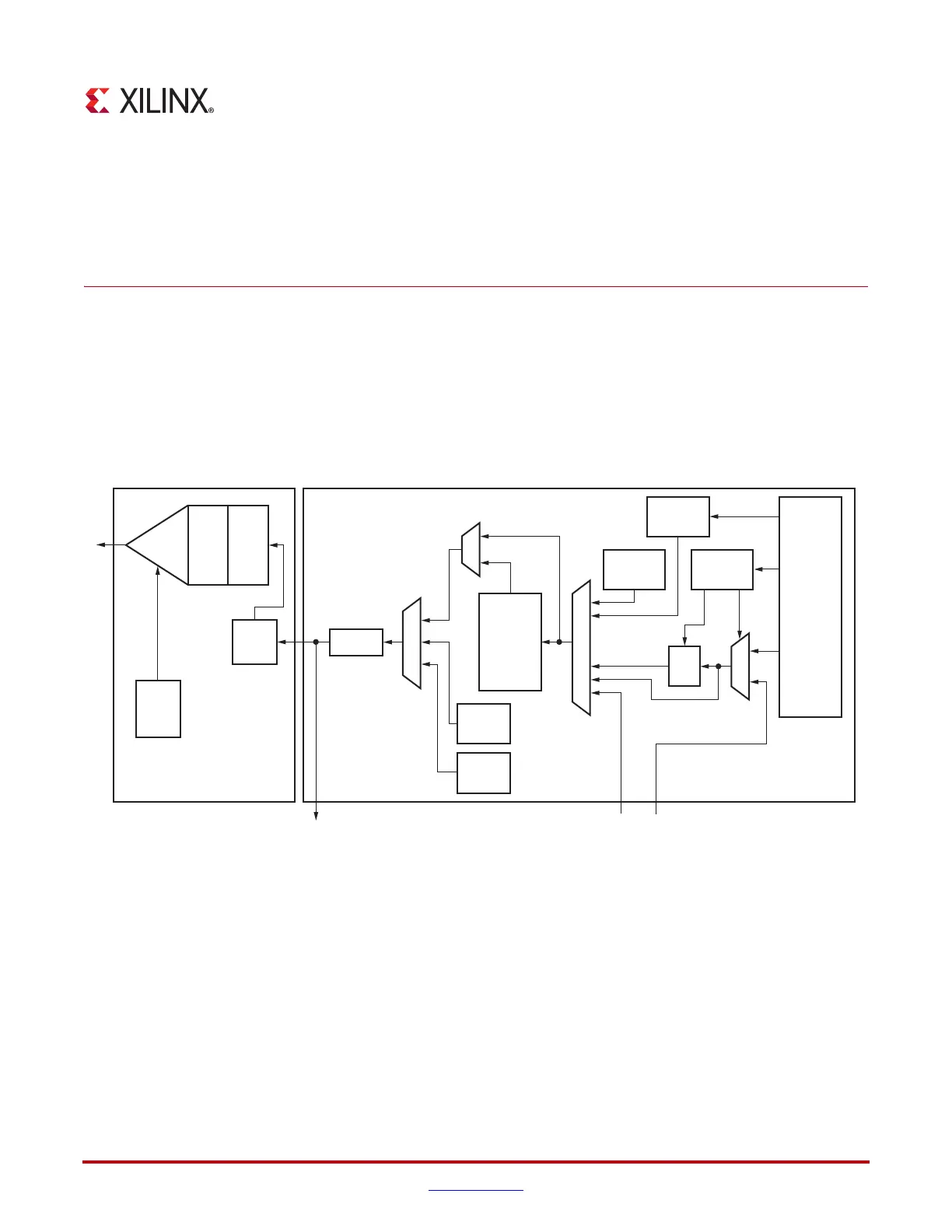

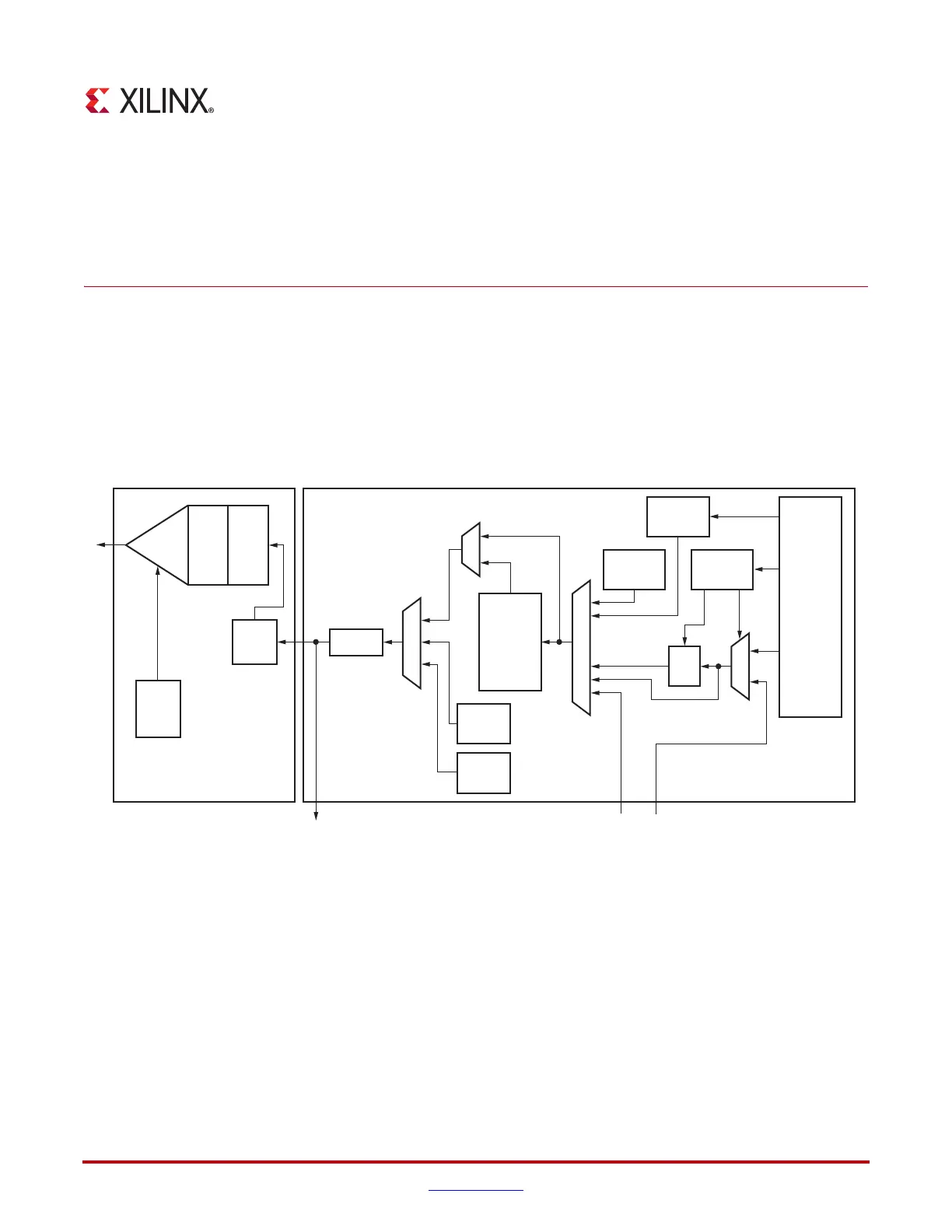

This chapter shows how to configure and use each of the functional blocks inside the GTX

transmitter (TX). Each GTX transceiver includes an independent transmitter, which

consists of a PCS and a PMA. Figure 3-1 shows the functional blocks of the transmitter.

Parallel data flows from the FPGA into the FPGA TX interface, through the PCS and PMA,

and then out the TX driver as high-speed serial data.

The key elements of the GTX TX are:

1. FPGA TX Interface, page 128

2. TX Initialization, page 136

3. TX 8B/10B Encoder, page 143

4. TX Gearbox, page 146

5. TX Buffer, page 153

6. TX Buffer Bypass, page 155

7. TX Pattern Generator, page 162

X-Ref Target - Figure 3-1

Figure 3-1: GTX TX Block Diagram

TX-PMA TX-PCS

FPGA

TX

Interface

TX

Gearbox

UG366_c3_01_051509

TX PIPE

Control

Phase

Adjust

FIFO &

Over-

sampling

PCIe

Beacon

From RX Parallel Data

(Far-End PMA Loopback)

To RX Parallel

Data (Near-End

PCS Loopback)

From RX Parallel Data

(Far-End PCS Loopback)

PISO

TX

Pre/

Post

emp

PMA

PLL

Divider

TX

OOB

and

PCIe

TX

Driver

Polarity

SATA

OOB

8B/

10B

Pattern

Generator

Loading...

Loading...