Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 117

UG366 (v2.5) January 17, 2011

PLL

PLL Settings for Common Protocols

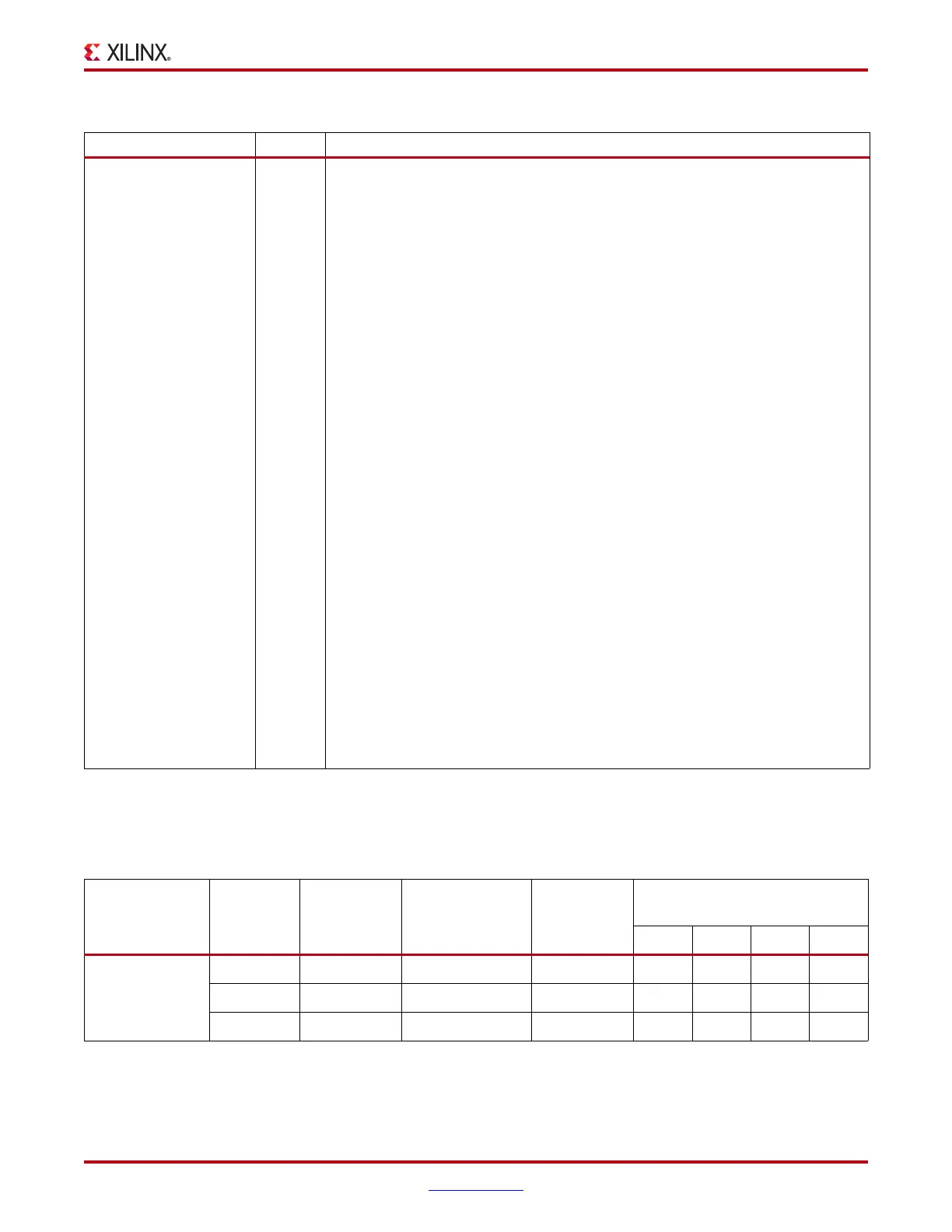

Table 2-10 shows example PLL divider settings for several standard protocols.

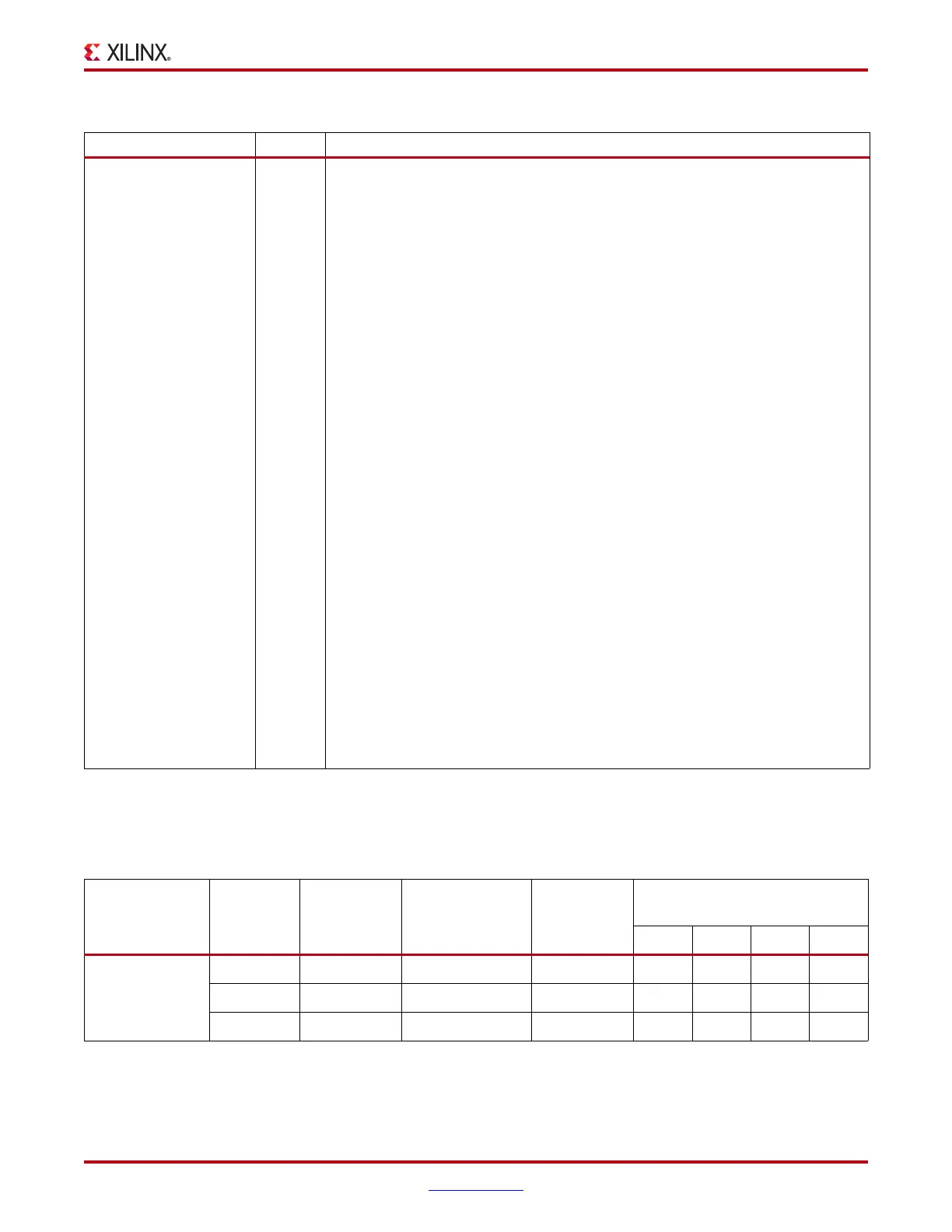

RX_CLK25_DIVIDER

TX_CLK25_DIVIDER

Integer This attribute is set to get an internal clock for the GTX channel:

1: CLKIN 25 MHz

2: 25 MHz < CLKIN 50 MHz

3: 50 MHz < CLKIN 75 MHz

4: 75 MHz < CLKIN 100 MHz

5: 100 MHz < CLKIN 125 MHz

6: 125 MHz < CLKIN 150 MHz

7: 150 MHz < CLKIN 175 MHz

8: 175 MHz < CLKIN 200 MHz

9: 200 MHz < CLKIN 225 MHz

10: 225 MHz < CLKIN 250 MHz

11: 250 MHz < CLKIN 275 MHz

12: 275 MHz < CLKIN 300 MHz

13: 300 MHz < CLKIN 325 MHz

14: 325 MHz < CLKIN 350 MHz

15: 350 MHz < CLKIN 375 MHz

16: 375 MHz < CLKIN 400 MHz

17: 400 MHz < CLKIN 425 MHz

18: 425 MHz < CLKIN 450 MHz

19: 450 MHz < CLKIN 475 MHz

20: 475 MHz < CLKIN 500 MHz

21: 500 MHz < CLKIN 525 MHz

22: 525 MHz < CLKIN 550 MHz

23: 550 MHz < CLKIN 575 MHz

24: 575 MHz < CLKIN 600 MHz

25: 600 MHz < CLKIN 625 MHz

26-32: Reserved

Table 2-9: PLL Attributes (Cont’d)

Attribute Type Description

Table 2-10: PLL Divider Settings for Common Protocols

Standard

Line Rate

[Gb/s]

Internal Data

Width

[16b/20b]

PLL Frequency

[GHz]

REFCLK

(Typical)

[MHz]

Using Typical REFCLK

Frequency

N1 N2 D M

Fibre Channel

(Single Rate)

4.25 20b 2.125 212.5 5211

2.125 20b 2.125 106.25 5421

1.0625 20b 2.125

106.25

5441

Loading...

Loading...