Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 247

UG366 (v2.5) January 17, 2011

RX Channel Bonding

RX Channel Bonding

Functional Description

The RX elastic buffer can also be used for channel bonding. Channel bonding cancels out

the skew between GTX transceiver lanes by using the RX elastic buffer as a variable latency

block. The transmitter sends a pattern simultaneously on all lanes, which the channel

bonding circuit uses to set the latency for each lane so that data is presented without skew

at the FPGA RX interface.

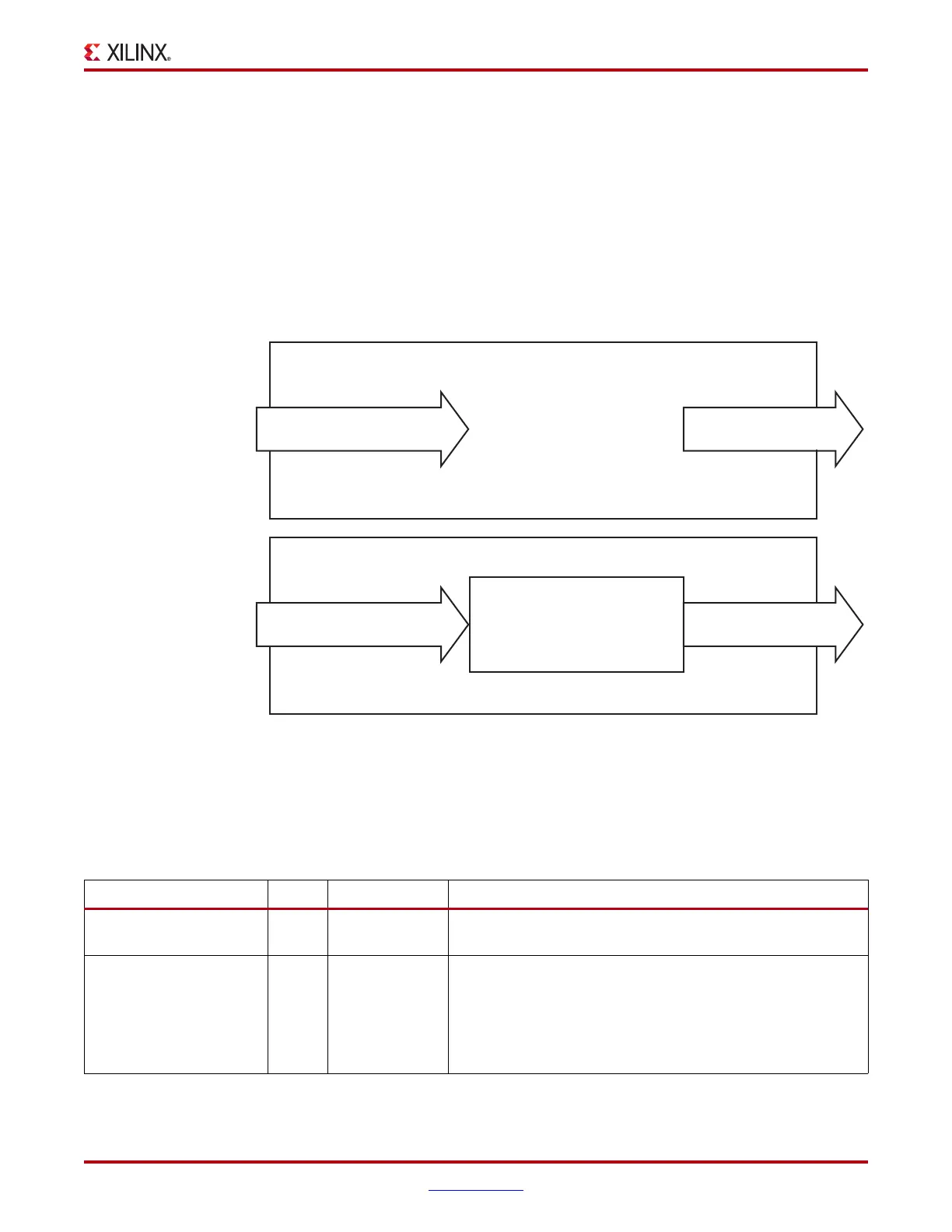

Figure 4-38 shows a conceptual view of channel bonding.

Ports and Attributes

Table 4-48 defines the RX channel bonding ports.

X-Ref Target - Figure 4-38

Figure 4-38: Channel Bonding Conceptual View

Deskewed Data

RX Data is Two Clock Cycles

Behind GTX0 Data

64 Element Elastic Buffer

(Set to Two Cycles of Latency by

Channel Bonding Controller)

UG366_c4_35_051509

GTX1 (Slave)

Deskewed Data

RX Data is Two Clock Cycles

Ahead of GTX1 Data

64 Element Elastic Buffer

(Set to Four Cycles of Latency by

Channel Bonding Controller)

GTX0 (Master)

Table 4-48: RX Channel Bonding Ports

Port Dir Clock Domain Description

RXCHANBONDSEQ Out RXUSRCLK2 This port goes High when RXDATA contains the start of a

channel bonding sequence.

RXCHANISALIGNED Out RXUSRCLK2 This signal from the RX elastic buffer goes High to indicate that

the channel is properly aligned with the master transceiver

according to observed channel bonding sequences in the data

stream. This signal goes Low if an unaligned channel bonding

sequence is detected, indicating that channel alignment was

lost.

Loading...

Loading...