Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 159

UG366 (v2.5) January 17, 2011

TX Buffer Bypass

• GTXTXRESET is asserted

•TXPLLPOWERDOWN is deasserted

• The clocking source changed

• The line rate of the GTX TX transceiver changed

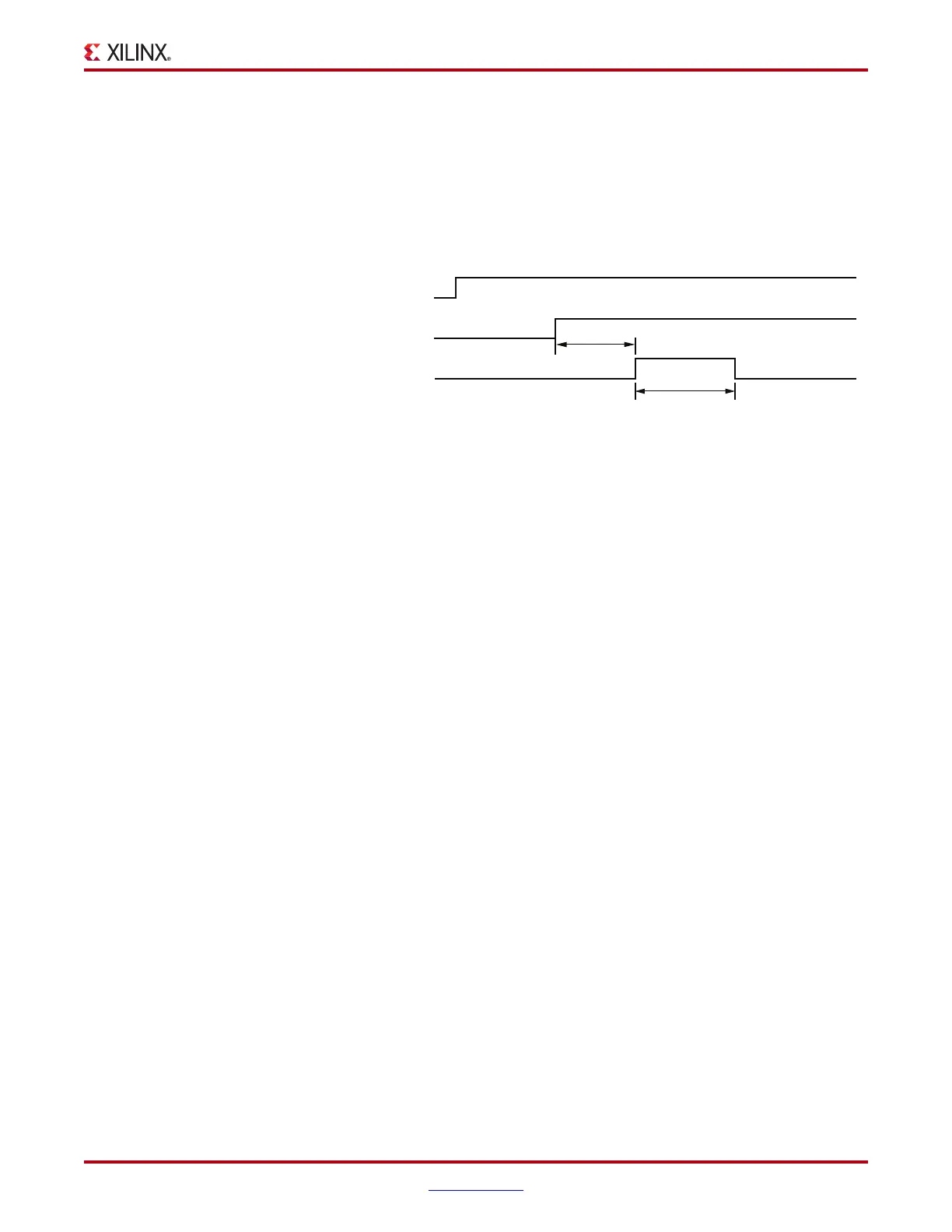

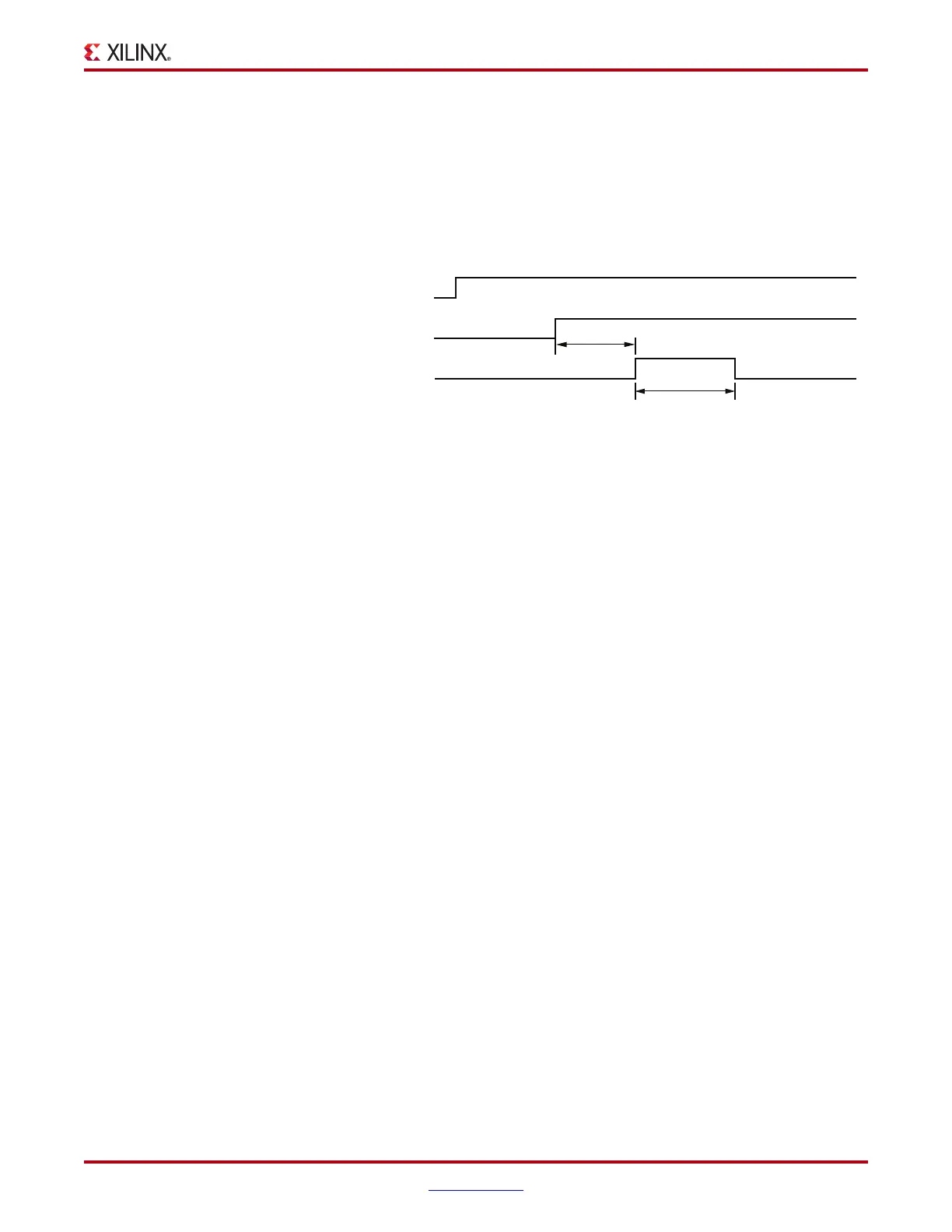

Figure 3-21 shows the TX phase-alignment procedure. See Table 3-20 for the required

TXUSRCLK2 clock cycles in asserting TXPMASETPHASE High.

TX Phase Alignment after Rate Change Use Mode

After a line rate change and if the TX buffer is bypassed, it is necessary to perform TX

phase alignment and reset the TX PLL output clock divider. The main difference between

the TX phase-alignment procedure after a reset and after a rate change is holding

TXENPMAPHASEALIGN asserted after the rate change.

The steps for an example TX phase-alignment after a rate change are:

1. In non PCI Express mode, a TX rate change completion occurs when a TXRATEDONE

pulse is detected.

In PCI Express mode, a TX rate change completion occurs when a PHYSTATUS pulse

is detected following a TXRATEDONE pulse.

After PHYSTATUS pulse is detected, assert GTXTEST[1] for 16 TXUSRCLK2 cycles to

reset the TX PLL output clock divider.

2. Hold TXENPMAPHASEALIGN asserted.

3. Wait for at least 32 TXUSRCLK2 cycles.

4. Assert TXPMASETPHASE for the required TXUSRCLK2 cycles specified in Table 3-20.

5. Assert the TXRESET pulse and wait for TXRESETDONE to be asserted.

6. For PCI Express mode, the “USER_PHYSTATUS” user signal must be generated and

used as PIPE PHYSTATUS. Under normal operation, USER_PHYSTATUS follows the

GTX PHYSTATUS signal. During rate change and subsequent TX phase alignment,

USER_PHYSTATUS must gate the GTX PHYSTATUS and delay its assertion until after

the TX phase alignment sequence is completed.

For non PCI Express mode, a “SYNC_DONE” user signal, which behaves like

USER_PHYSTATUS, can be asserted to indicate TX phase-alignment completion.

Figure 3-22 shows the TX phase alignment after a rate change.

X-Ref Target - Figure 3-21

Figure 3-21: TX Phase Alignment Procedure after GTXTXRESET

TXRESETDONE

TXENPMAPHASEALIGN

TXPMASETPHASE

32 TXUSRCLK2 Cycles

Required TXUSRCLK2 Cycles

UG366_c3_11_122810

Loading...

Loading...