Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 239

UG366 (v2.5) January 17, 2011

RX Elastic Buffer

Ports and Attributes

Table 4-43 defines the RX elastic buffer ports.

Table 4-44 defines the RX elastic buffer attributes.

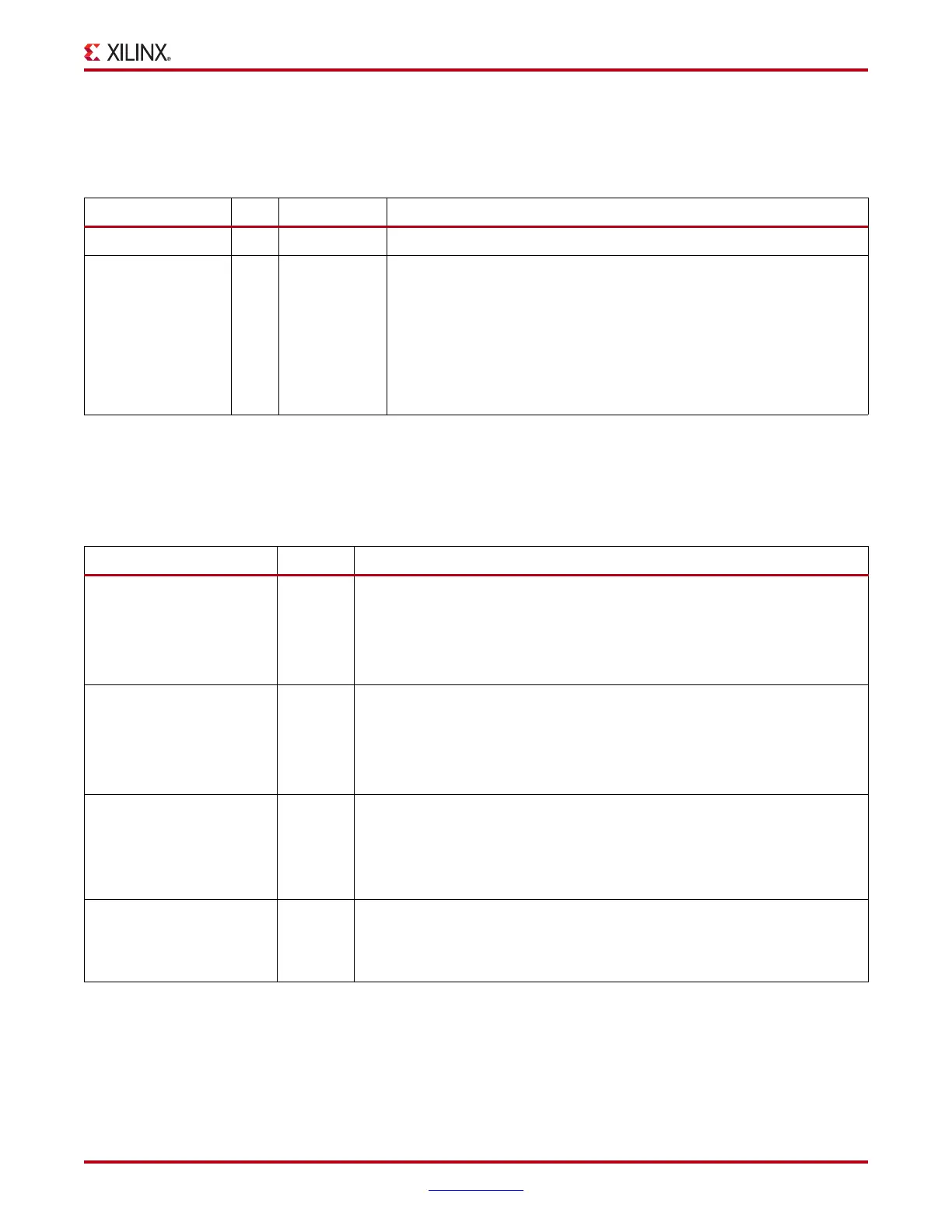

Table 4-43: RX Elastic Buffer Ports

Port Dir Clock Domain Description

RXBUFRESET In Async Resets the RX elastic buffer logic and re-initializes the RX elastic buffer.

RXBUFSTATUS[2:0] Out RXUSRCLK2 Indicates the status of the RX elastic buffer as follows:

000: Nominal condition

001: Number of bytes in the buffer are less than CLK_COR_MIN_LAT

010: Number of bytes in the buffer are greater than

CLK_COR_MAX_LAT

101: RX elastic buffer underflow

(1)

110: RX elastic buffer overflow

(1)

Notes:

1. If an RX elastic buffer overflow or an RX elastic buffer underflow condition occurs, the content of the RX elastic buffer becomes

invalid, and the RX elastic buffer needs re-initialization by asserting/deasserting RXBUFRESET.

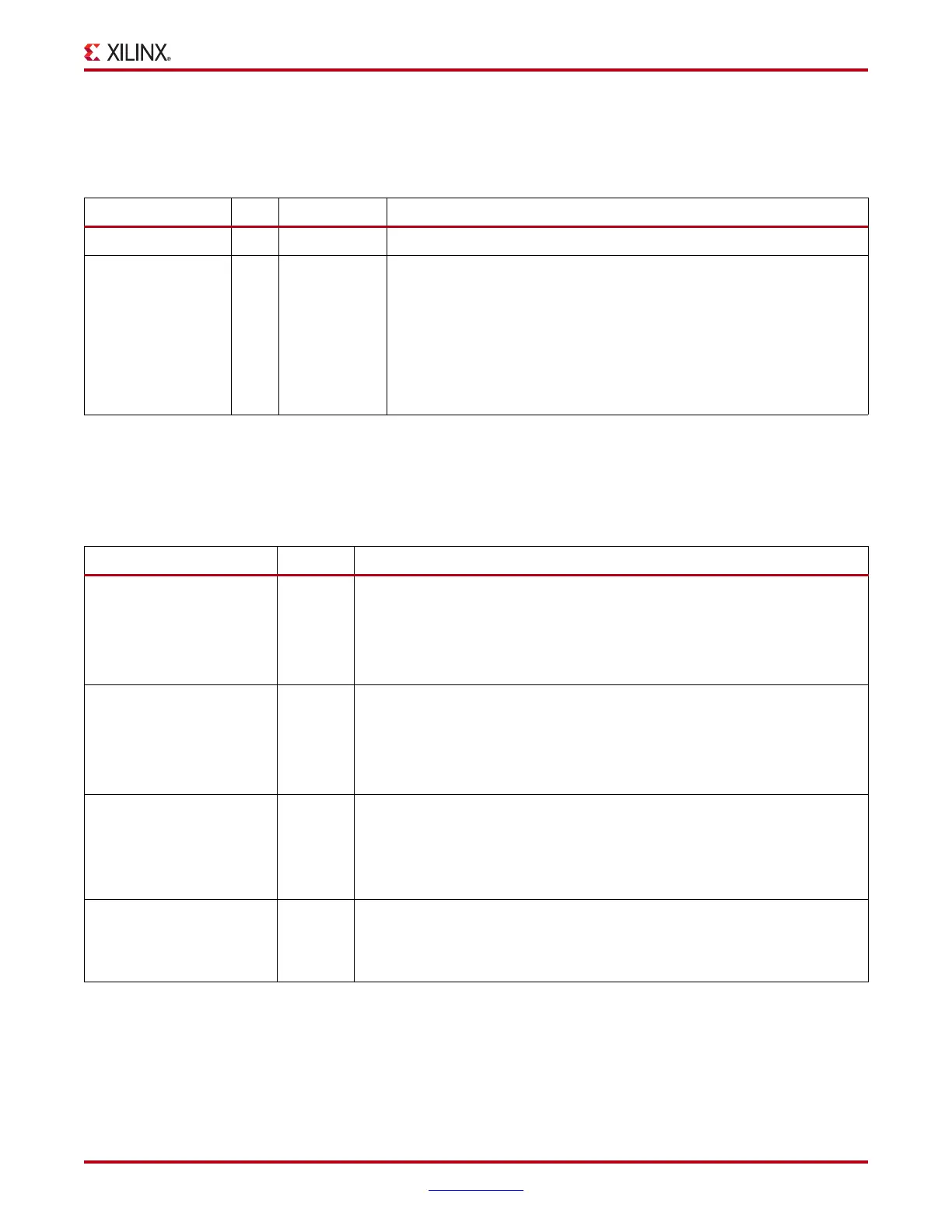

Table 4-44: RX Elastic Buffer Attributes

Attribute Type Description

RX_BUFFER_USE Boolean Use or bypass the RX elastic buffer.

TRUE: Use the RX elastic buffer (normal mode).

FALSE: Permanently bypass the RX elastic buffer (advanced feature). If

OVERSAMPLE_MODE is FALSE, RX phase alignment must be used

whenever the RX elastic buffer is bypassed.

RX_EN_IDLE_RESET_BUF Boolean Enable or disable the automatic RX elastic buffer reset.

TRUE: Enable the automatic RX elastic buffer reset when valid signals are

not present on the RXN/RXP inputs.

FALSE: Disable the automatic RX elastic buffer reset when valid signals are

not present on the RXN/RXP inputs.

RX_FIFO_ADDR_MODE String FULL: Enable the RX elastic buffer for clock correction and channel

bonding support. The maximum frequency is limited.

FAST: Enable the RX elastic buffer for phase compensation without clock

correction and channel bonding support. This mode is recommended for

high line rates.

RX_IDLE_HI_CNT 4-bit

Binary

Determines count value after which an assertion of reset due to

RX_EN_IDLE_RESET_BUF is triggered after valid data is no longer present

on the RXP/RXN lines. Use the Virtex-6 FPGA GTX Transceiver Wizard

default.

Loading...

Loading...