184 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

6. RX Margin Analysis, page 210

7. RX Polarity Control, page 213

8. RX Oversampling, page 214

9. RX Pattern Checker, page 215

10. RX Byte and Word Alignment, page 217

11. RX Loss-of-Sync State Machine, page 226

12. RX 8B/10B Decoder, page 228

13. RX Buffer Bypass, page 231

14. RX Elastic Buffer, page 238

15. RX Clock Correction, page 240

16. RX Channel Bonding, page 247

17. RX Gearbox, page 256

18. RX Initialization, page 261

19. FPGA RX Interface, page 269

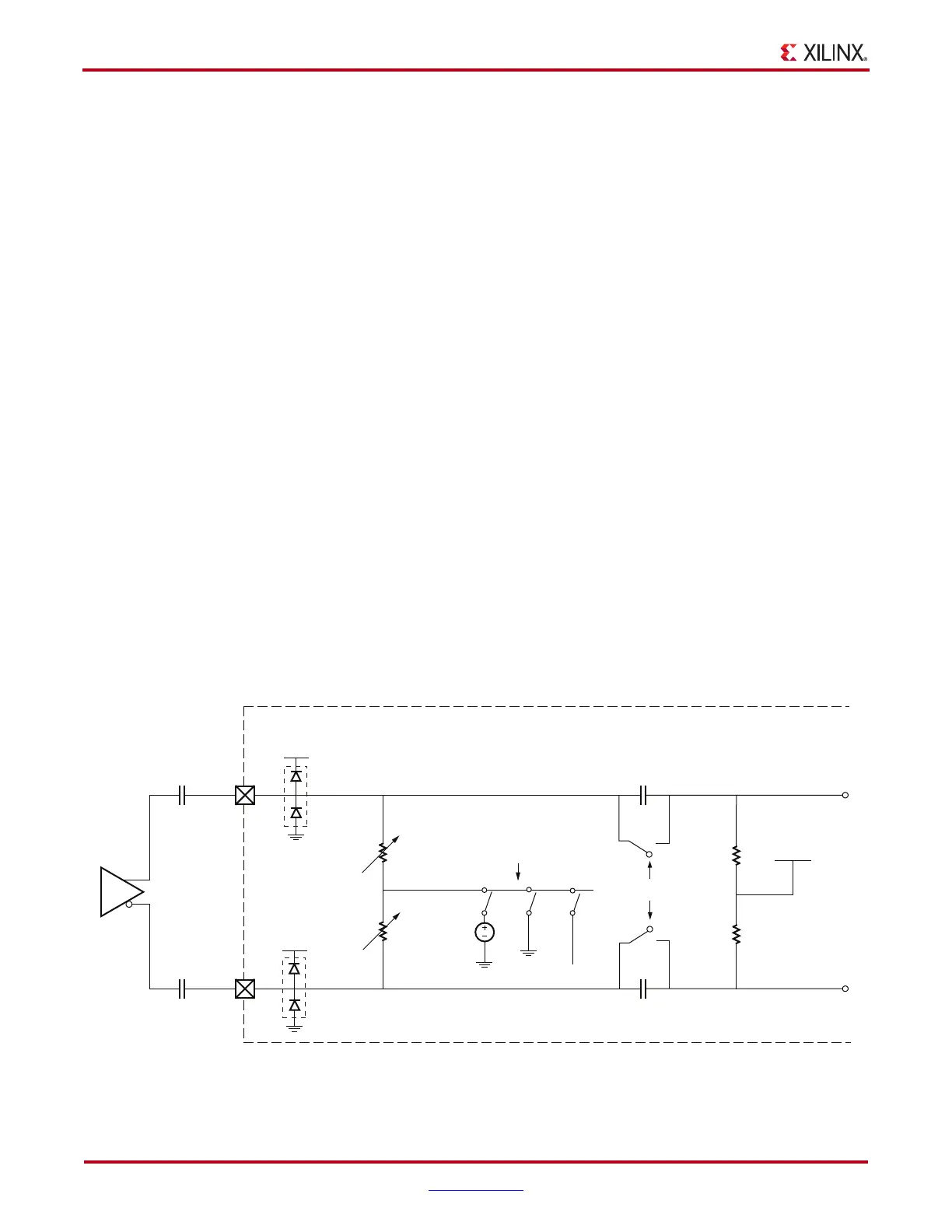

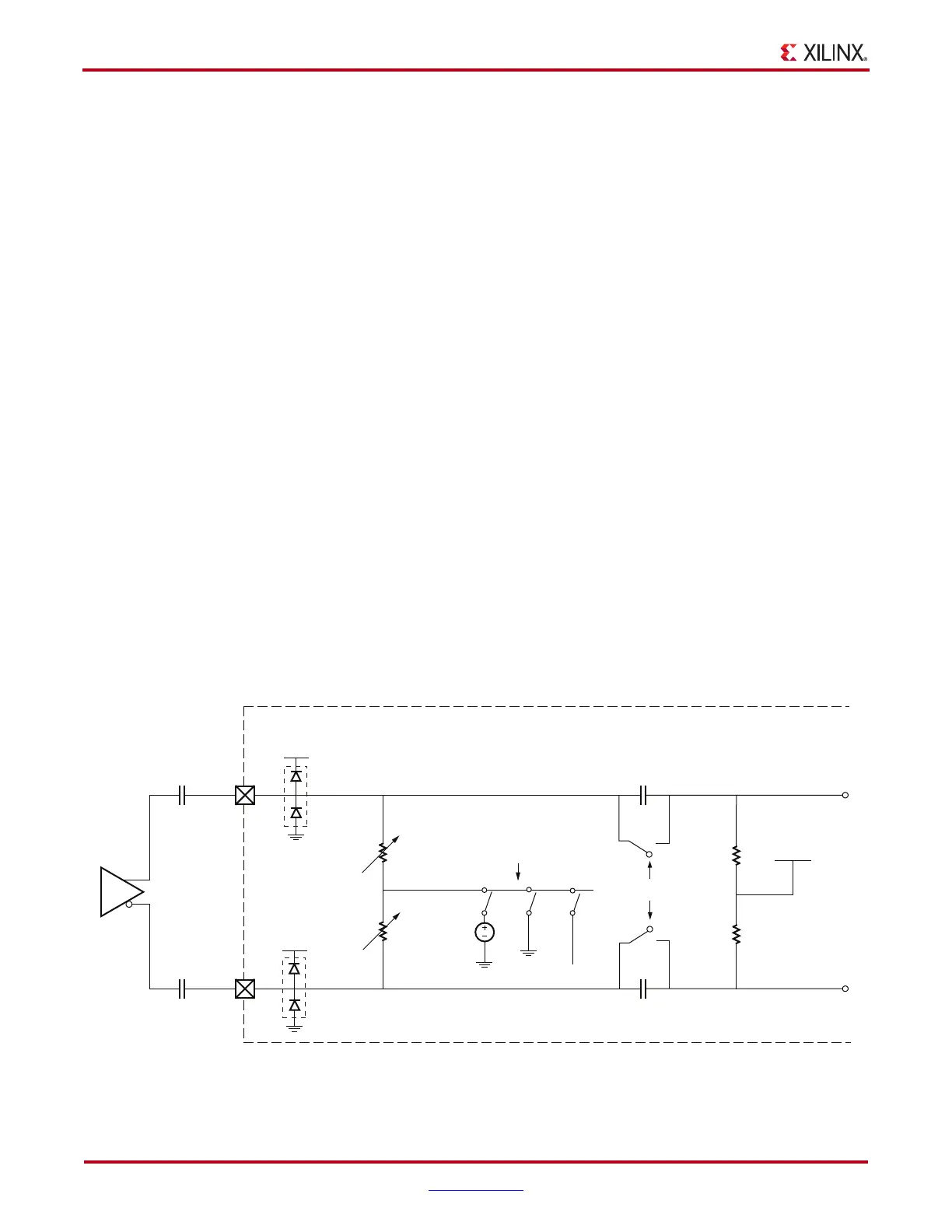

RX Analog Front End

Functional Description

The RX analog front end (AFE) is a high-speed current-mode input differential buffer. It

has the following features

• Configurable RX termination voltage

• Bypassable on-chip coupling capacitors

• Calibrated termination resistors

X-Ref Target - Figure 4-2

Figure 4-2: RX AFE Block Diagram

UG366_c4_02_081109

~100 nF

nominal

50

Ω

nominal

50

Ω

FPGABoard

MGTAVTT_*

MGTAVTT_*

MGTAVTT_*

FLOAT

GND

RCV_TERM_VTTRX

RCV_TERM_GND

~100 nF

AC_CAP_DIS

nominal 7 pF

nominal 7 pF

ESD Diodes

ESD Diodes

nominal

50 KΩ

nominal

50 KΩ

V

CM

2/3 MGTAVTT_*

Loading...

Loading...