166 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

TX Oversampling

Functional Description

Each GTX transceiver includes built-in 5X oversampling to enable serial rates from 1/10

th

of the lower border of the frequency range of the TX PMA PLL up to 4/10th of the TX PMA

PLL. The digital oversampling circuit takes parallel data from the user interface at five

times the desired line rate and replicates the data bit five times before advancing to the

next bit. The internal data width is automatically set to 20 bits when TX oversampling is

enabled.

Ports and Attributes

There are no TX oversampling ports.

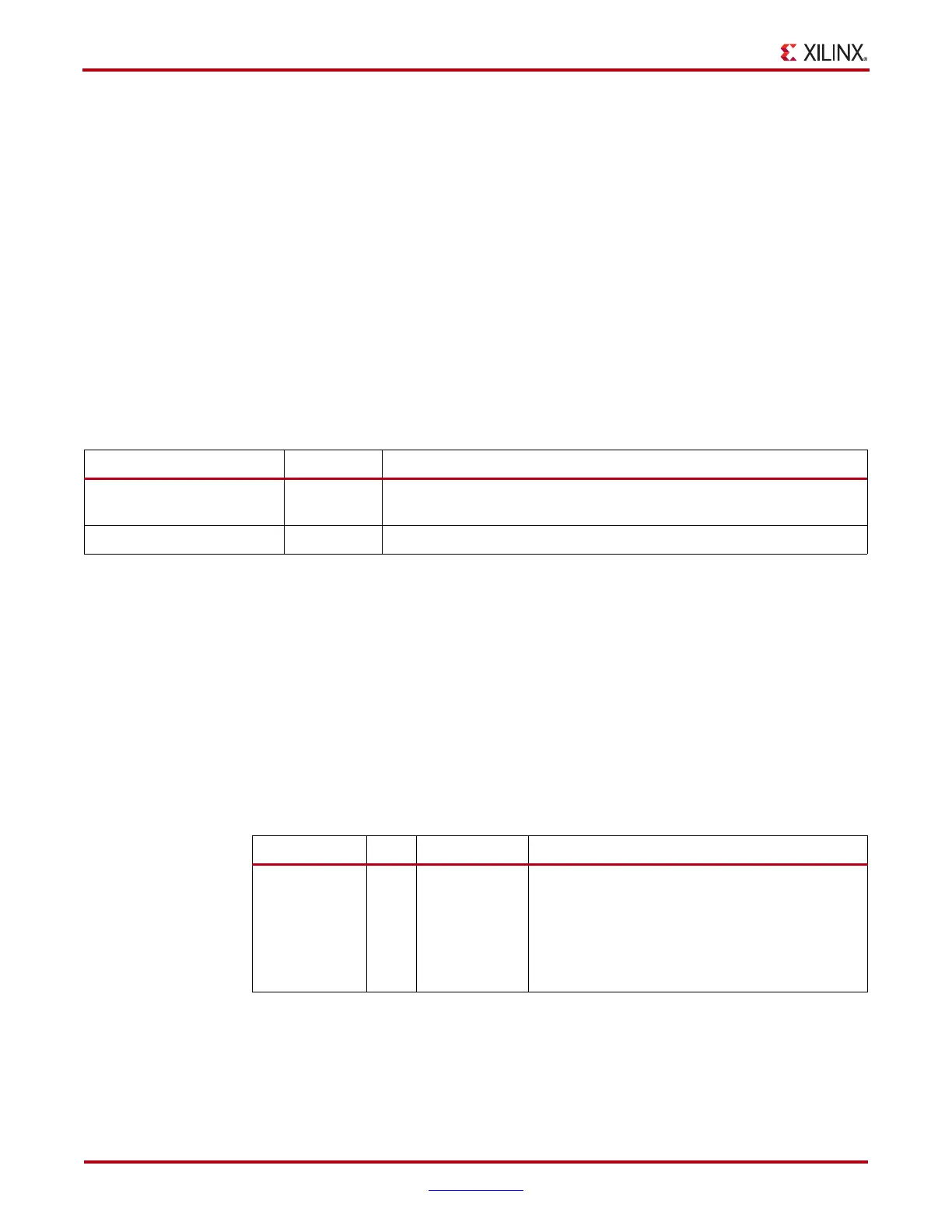

Table 3-26 defines the TX oversampling attributes.

TX Polarity Control

Functional Description

The GTX transceiver includes a TX polarity control function to invert outgoing data from

the PCS before serialization and transmission. The TXPOLARITY port is driven High to

invert the polarity of outgoing data.

Ports and Attributes

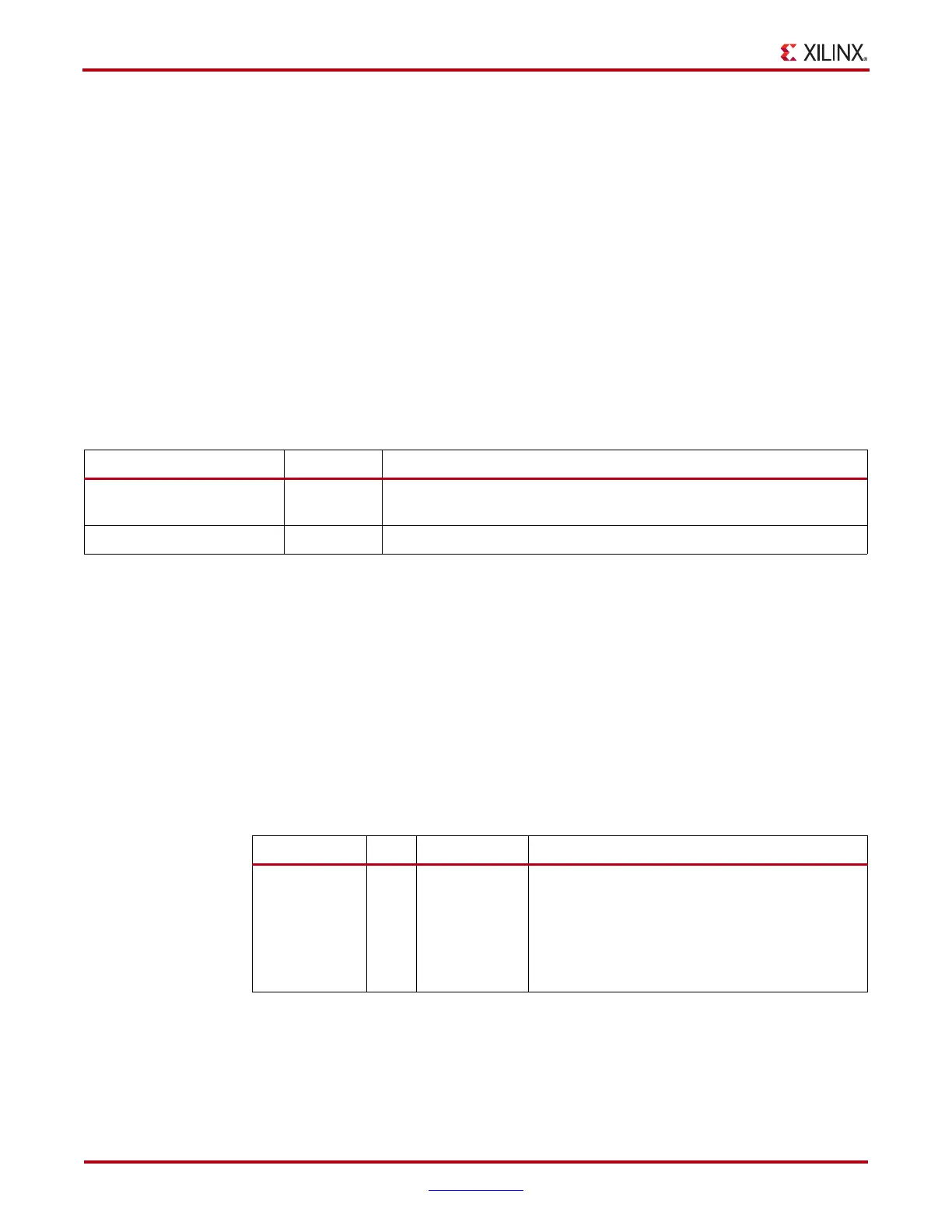

Table 3-27 defines the TX polarity control ports.

There are no TX polarity control attributes.

Using TX Polarity Control

If the TXP/TXN differential traces are swapped on a board, tie TXPOLARITY High.

Table 3-26: TX Oversampling Attributes

Attribute Type Description

TX_OVERSAMPLE_MODE Boolean This enables transmitter oversampling when TRUE, and 5X

oversampling is On.

TXPLL_DIVSEL_OUT Integer TXPLL_DIVSEL_OUT must be set to 1 when using oversampling mode.

Table 3-27: TX Polarity Control Ports

Port Dir Clock Domain Description

TXPOLARITY In TXUSRCLK2 The TX polarity port is used to invert the polarity

of outgoing data.

0: Not inverted. TXP is positive, and TXN is

negative.

1: Inverted. TXP is negative, and TXN is

positive.

Loading...

Loading...