Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 185

UG366 (v2.5) January 17, 2011

RX Analog Front End

Note: MGTAVTT_* refers to MGTAVTT_S of the south package power plane and MGTAVTT_N of

the north package power plane, as outlined in Figure 5-4, page 277.

Ports and Attributes

Table 4-1 defines the RX AFE ports.

Table 4-2 defines the RX analog front end attributes.

Table 4-1: RX AFE Ports

Port Dir Clock Domain Description

RXN

RXP

In

(Pad)

RX Serial Clock RXN and RXP are differential complements of one another forming

a differential receiver input pair. These ports represent pads. The

location of these ports must be constrained (see Implementation,

page 41) and brought to the top level of the design.

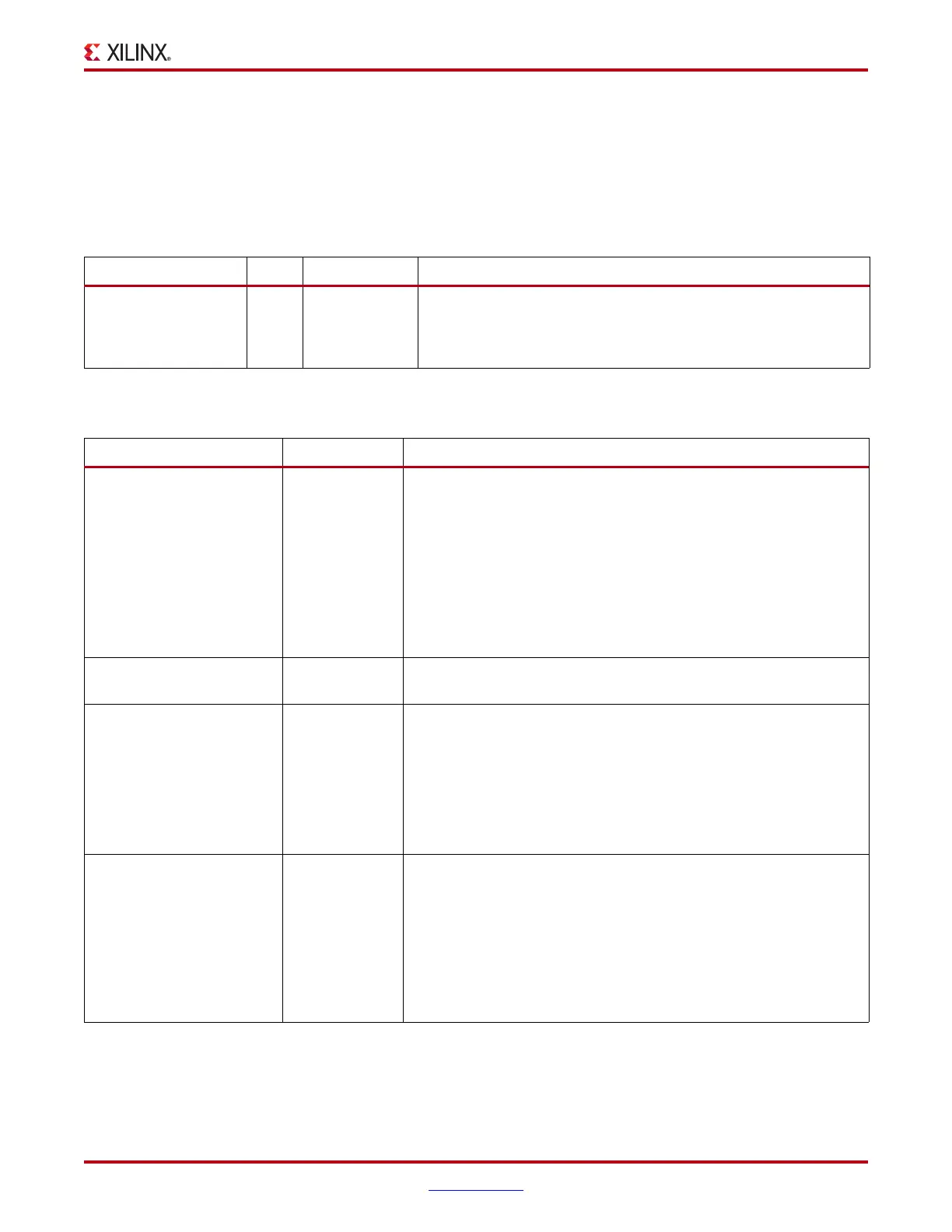

Table 4-2: RX AFE Attributes

Attribute Type Description

AC_CAP_DIS Boolean Bypasses the built-in AC coupling in the receiver.

TRUE: Built-in AC coupling capacitors are bypassed. DC coupling

to the receiver is possible.

FALSE: Built-in AC coupling capacitors are enabled.

See Chapter 5, Board Design Guidelines, for details about when it is

appropriate to add an additional external AC coupling capacitor

based on data rate or protocol.

See Use Modes – RX Termination for valid RX Termination

combinations.

CM_TRIM[1:0] 2-bit Binary Adjusts the input common mode levels. These levels are automatically

set in the Virtex®-6 FPGA GTX Transceiver Wizard.

RCV_TERM_GND Boolean Activates the Ground reference for the receiver termination network.

The default for this attribute is TRUE for PCI Express designs.

Generally, for all other protocols, the default setting is FALSE.

TRUE: Ground reference for receiver termination activated.

FALSE: Ground reference for receiver termination disabled.

See Use Modes – RX Termination for valid RX Termination

combinations.

RCV_TERM_VTTRX Boolean Activates the MGTAVTT_* reference for the receiver termination

network. The default for this attribute is FALSE for PCI Express

designs. For all other protocols, the default setting is TRUE. The

setting is FALSE when using AC coupling.

TRUE: MGTAVTT_* reference for receiver termination activated.

FALSE: MGTAVTT_* reference for receiver termination disabled.

See Use Modes – RX Termination for valid RX Termination

combinations.

Loading...

Loading...