Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 181

UG366 (v2.5) January 17, 2011

TX Out-of-Band Signaling

The GTX transceiver supports beaconing as described in the PHY Interface for the PCI

Express (PIPE) Specification. The format of the beacon sequence is controlled by the FPGA

logic.

Ports and Attributes

Table 3-34 defines the TX OOB ports.

Table 3-35 defines the TX OOB attributes.

The GTX transceiver supports four signaling modes: three for SATA/SAS operations and

one for PCI Express operations. The use of these mechanisms is mutually exclusive.

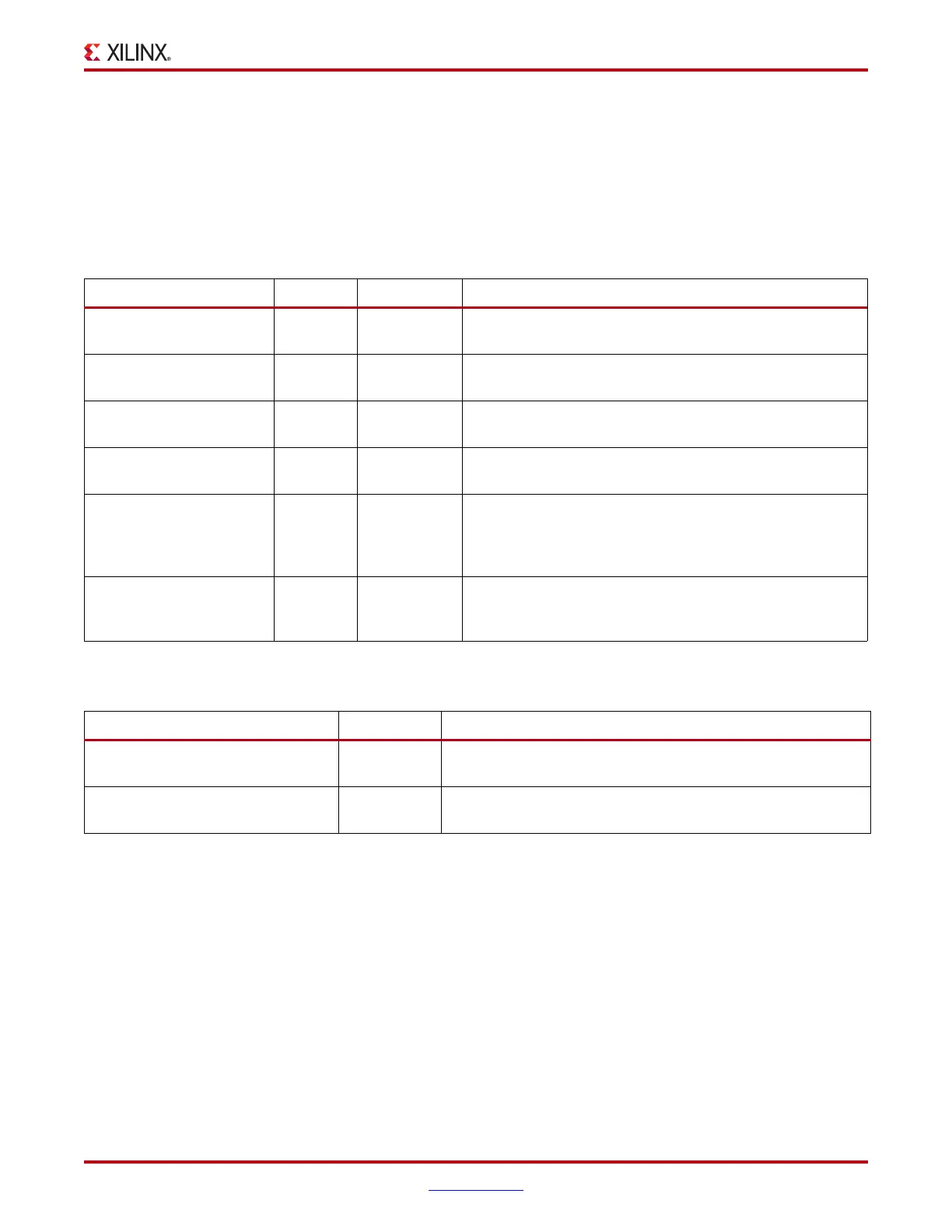

Table 3-34: TX OOB Ports

Port Direction Clock Domain Description

COMFINISH Out TXUSRCLK2 This output indicates completion of transmission of the last

SAS or SATA TXCOM sequence.

TXCOMINIT In TXUSRCLK2 This input initiates the transmission of the TXCOMINIT

sequence.

TXCOMSAS In TXUSRCLK2 This input initiates the transmission of the TXCOMSAS

sequence.

TXCOMWAKE In TXUSRCLK2 This input initiates the transmission of the TXCOMWAKE

sequence.

TXELECIDLE In TXUSRCLK2 When in the PCIe P2 power state, this signal controls

whether an electrical idle or a beacon indication is driven

onto the TX pair. When in SATA mode, keep TXELECIDLE

High for generating SATA/SAS OOB COM signaling.

TXPOWERDOWN[1:0] In TXUSRCLK2 This input powers down the TX lanes. It is primarily used for

PCIe designs. Use TXPOWERDOWN = 00 for operating

SATA OOB signaling.

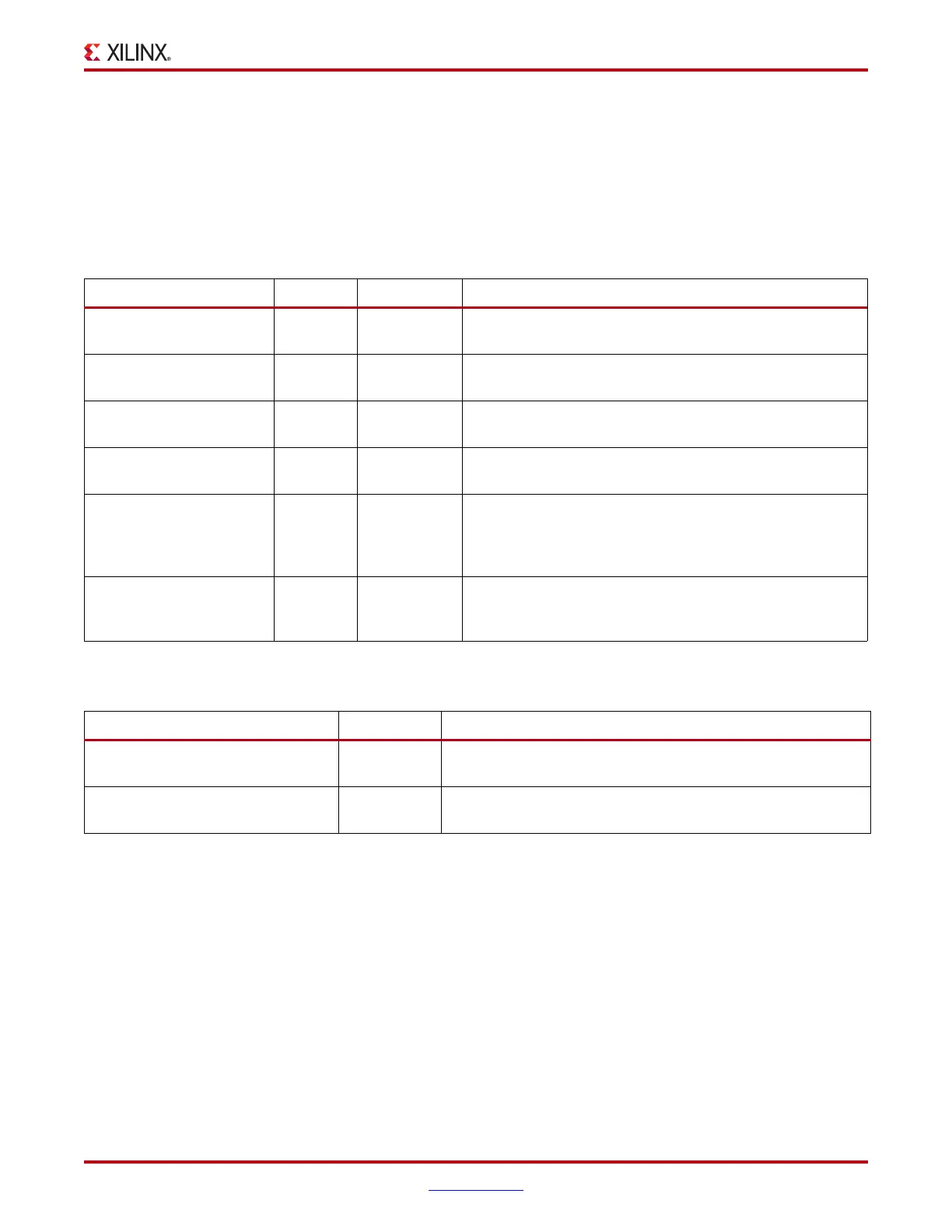

Table 3-35: TX OOB Attributes

Attribute Type Description

COM_BURST_VAL 4-bit Binary This attribute determines the number of bursts in a COM

sequence.

TXPLL_SATA 2-bit Binary Reserved. Use only recommended values from the

Virtex-6 FPGA GTX Transceiver Wizard.

Loading...

Loading...