38 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 1: Transceiver and Tool Overview

SecureIP models use a Verilog standard. To use them in a VHDL design, a mixed-

language simulator is required. The simulator must be capable of simulating VHDL

and Verilog simultaneously.

•Installed GTX SecureIP model.

• Correct setup of the simulator for SecureIP use (initialization file, environment

variable(s)).

• Running COMPXLIB (which compiles the simulation libraries (e.g. UNISIM,

SIMPRIMS, etc.) in the correct order.

• Correct simulator resolution (Verilog)

• The user guide of the simulator and the Synthesis and Simulation Design Guide provide

a detailed list of settings for SecureIP support.

Ports and Attributes

There are no simulation-only ports.

The GTXE1 primitive has attributes intended only for simulation. Ta ble 1-2 lists the

simulation-only attributes of the GTXE1 primitive. The names of these attributes start with

SIM_.

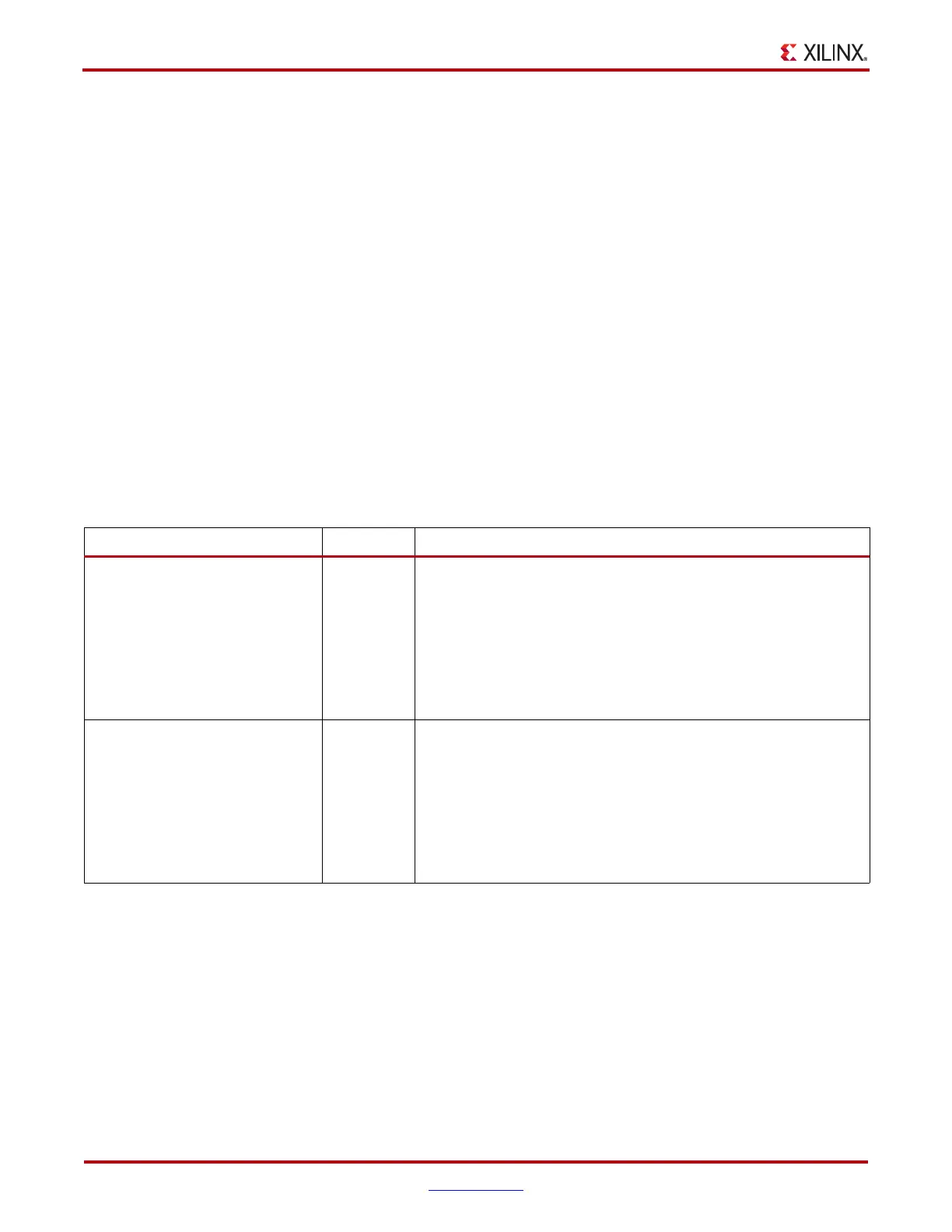

Table 1-2:

GTXE1 Simulation-Only Attributes

Attribute Type Description

SIM_GTXRESET_SPEEDUP Integer This attribute shortens the time it takes to finish the GTXRXRESET

and GTXTXRESET sequence and lock the TX PMA PLL and RX

PMA PLL during simulation.

0: The GTXRXRESET and GTXTXRESET sequence is simulated

with its original duration (standard initialization is

approximately 160 µs).

1: Shorten the GTXRXRESET and GTXTXRESET cycle time (fast

initialization is approximately 300 ns).

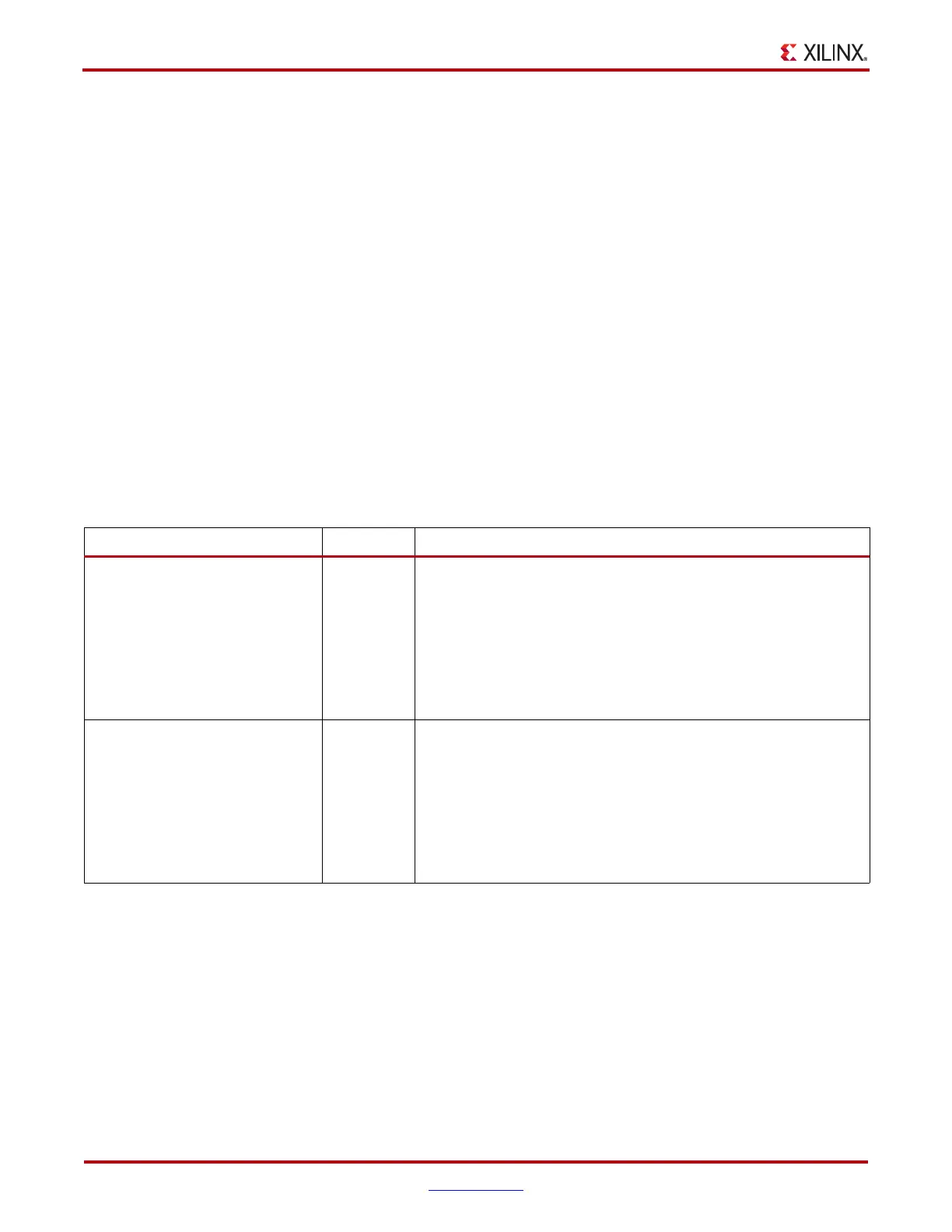

SIM_RECEIVER_DETECT_PASS Boolean This attribute simulates the TXDETECTRX feature in the

GTX

transceiver.

TRUE: Simulates an RX connection to the TX serial ports.

TXDETECTRX initiates receiver detection, and

RXSTATUS[2:0] = 011 reports that an RX port is connected.

FALSE (default): Simulates a disconnected TX port.

TXDETECTRX initiates receiver detection, and

RXSTATUS[2:0] = 000 reports that an RX port is not connected.

Loading...

Loading...