Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 261

UG366 (v2.5) January 17, 2011

RX Initialization

RX Initialization

Functional Description

The GTX RX must be reset before it can be used. There are three ways to reset the GTX RX:

1. Power up and configure the FPGA. Power-up reset is covered in this section.

2. Drive the GTXRXRESET port High to trigger a full asynchronous reset of the GTX RX.

3. Assert one or more of the individual reset signals on the block to reset a specific

subcomponent of the receiver. These resets are covered in detail in the sections for each

subcomponent (refer to Table 4-54, page 265).

All the reset ports described in this section initiate the internal receiver reset state machines

when driven High. The internal reset state machines are held in the reset state until these

same reset ports are driven Low. The completion of these state machines is signaled

through the RXRESETDONE port.

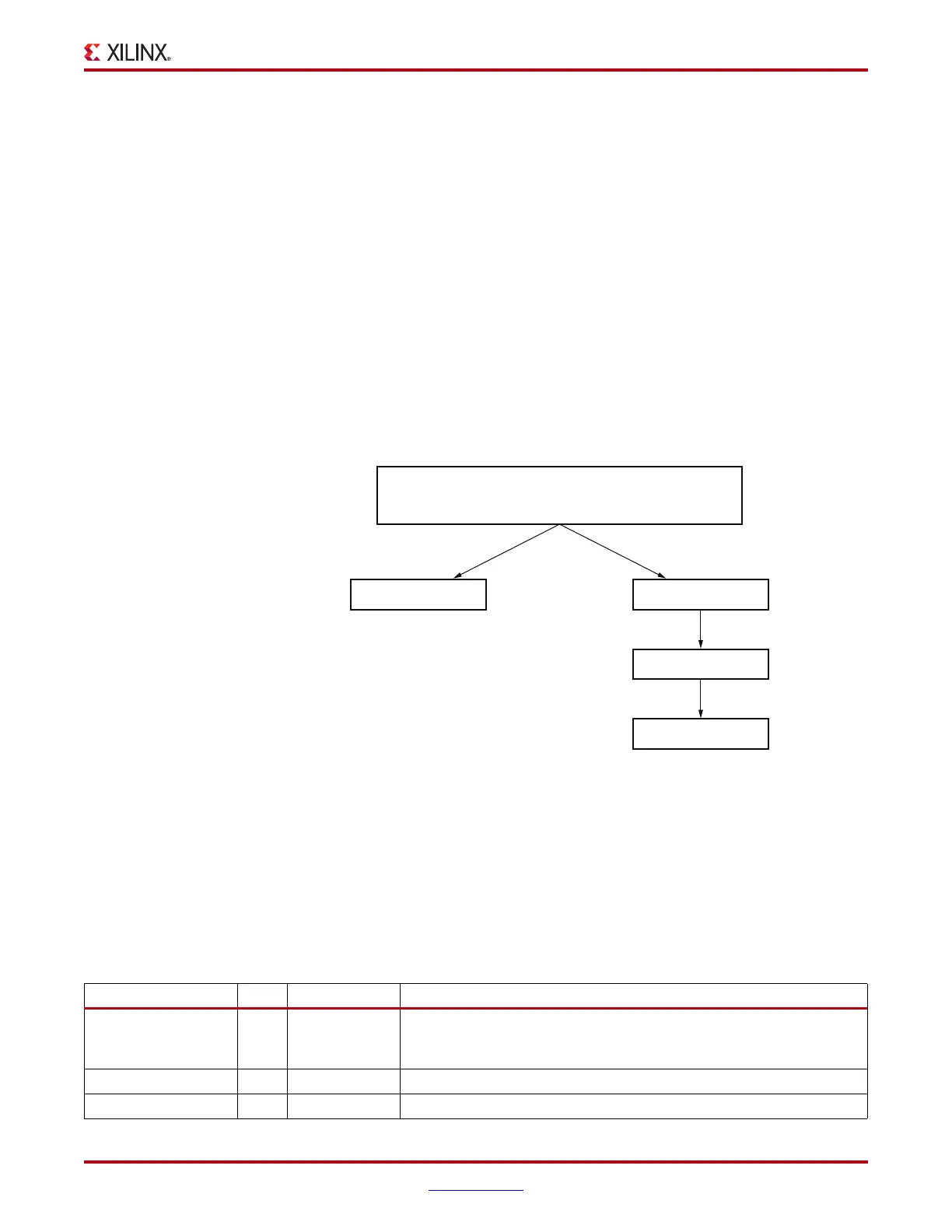

Figure 4-49 shows the GTX RX reset hierarchy.

When bypassing the TX buffer or the RX buffer, GTXRXRESET and PLLRXRESET must not

be tied High. Refer to TX Buffer Bypass, page 155 and RX Buffer Bypass, page 231 for more

information.

Ports and Attributes

Table 4-52 defines the RX initialization ports.

X-Ref Target - Figure 4-49

Figure 4-49: GTX RX Reset Hierarchy

After Configuration or GTXRXRESET or

Falling RXPLLPOWERDOWN

PLLRXRESET RXCDRRESET

RXRESET

RXBUFRESET

UG366_c4_46_061309

Table 4-52: RX Initialization Ports

Port Dir Clock Domain Description

GTXRXRESET In Async This port is asserted High and then deasserted to start the full RX GTX

reset sequence. This sequence takes about 120 µs to complete, and

systematically resets all subcomponents of the GTX RX.

PLLRXRESET In Async This port resets the RX PLL of the GTX RX.

PRBSCNTRESET In RXUSRCLK2 This port resets the PRBS error counter.

Loading...

Loading...