262 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

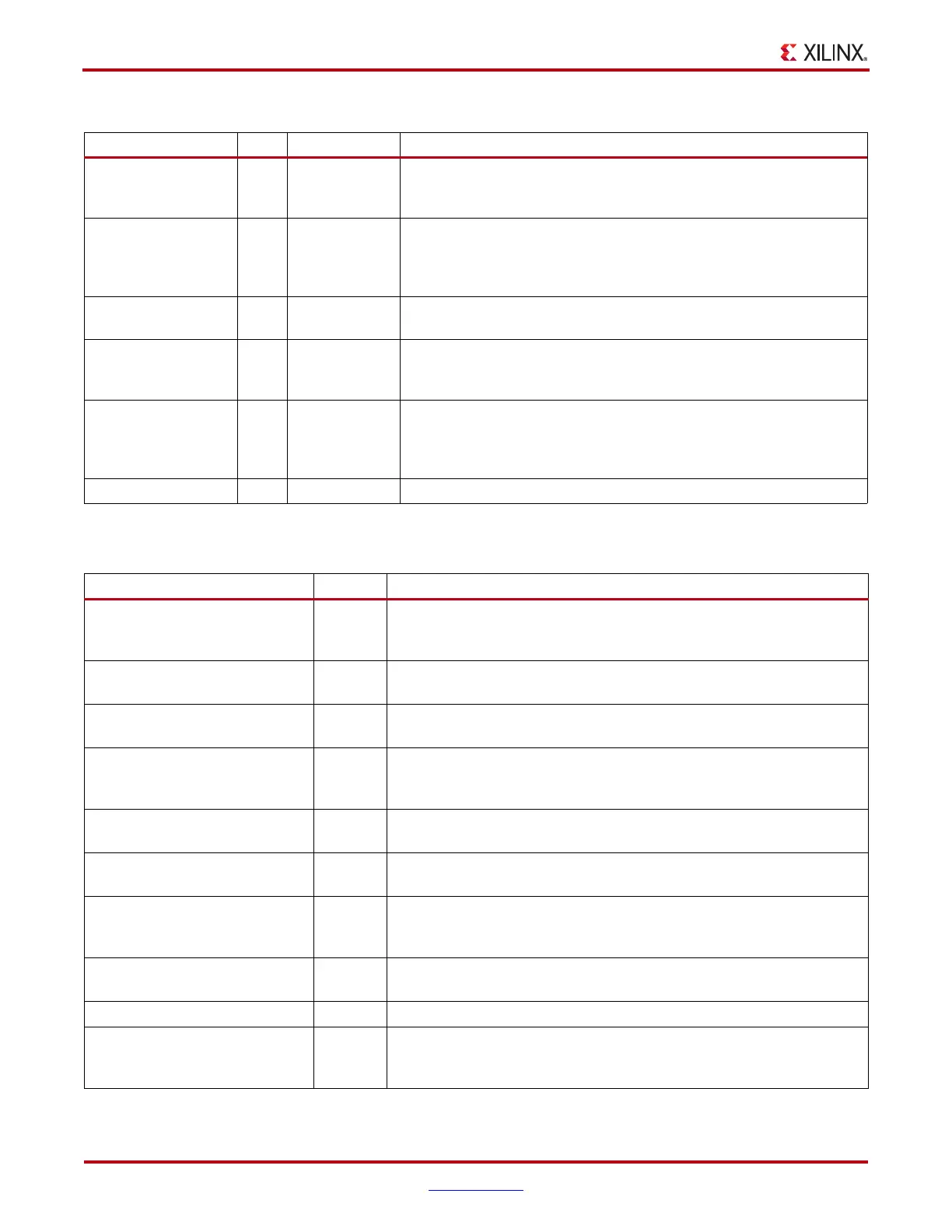

Table 4-53 defines the RX initialization attributes.

RXBUFRESET In Async PCS RX elastic buffer reset. This active-High signal resets the RX elastic

buffer logic; it resets the pointers in the buffer and flushes the data out

of the buffer.

RXCDRRESET In Async This port resets the CDR and the RX part of the PCS. This signal is

driven High to cause the CDR to give up its current lock and return to

the PMA PLL frequency. This port does not reset the PLL nor the PMA

low latency clock alignment.

RXDLYALIGNRESET In Async This port resets the RX delay aligner for the RX buffer bypass mode.

See RX Buffer Bypass, page 231.

RXRESET In Async PCS RX system reset. Resets receiver elastic buffer, 8B/10B decoder,

comma detect and other receiver registers. This reset is a subset of

GTXRXRESET and RXCDRRESET.

RXRESETDONE Out Async This port goes High when the GTX RX has finished reset and is ready

for use. For this signal to work correctly, the RX reference clock and all

clock inputs on the individual GTX RX (RXUSRCLK, RXUSRCLK2)

must be driven.

TSTIN[19:0] In Async Reserved. Must be tied to 11111111111111111111.

Table 4-52: RX Initialization Ports (Cont’d)

Port Dir Clock Domain Description

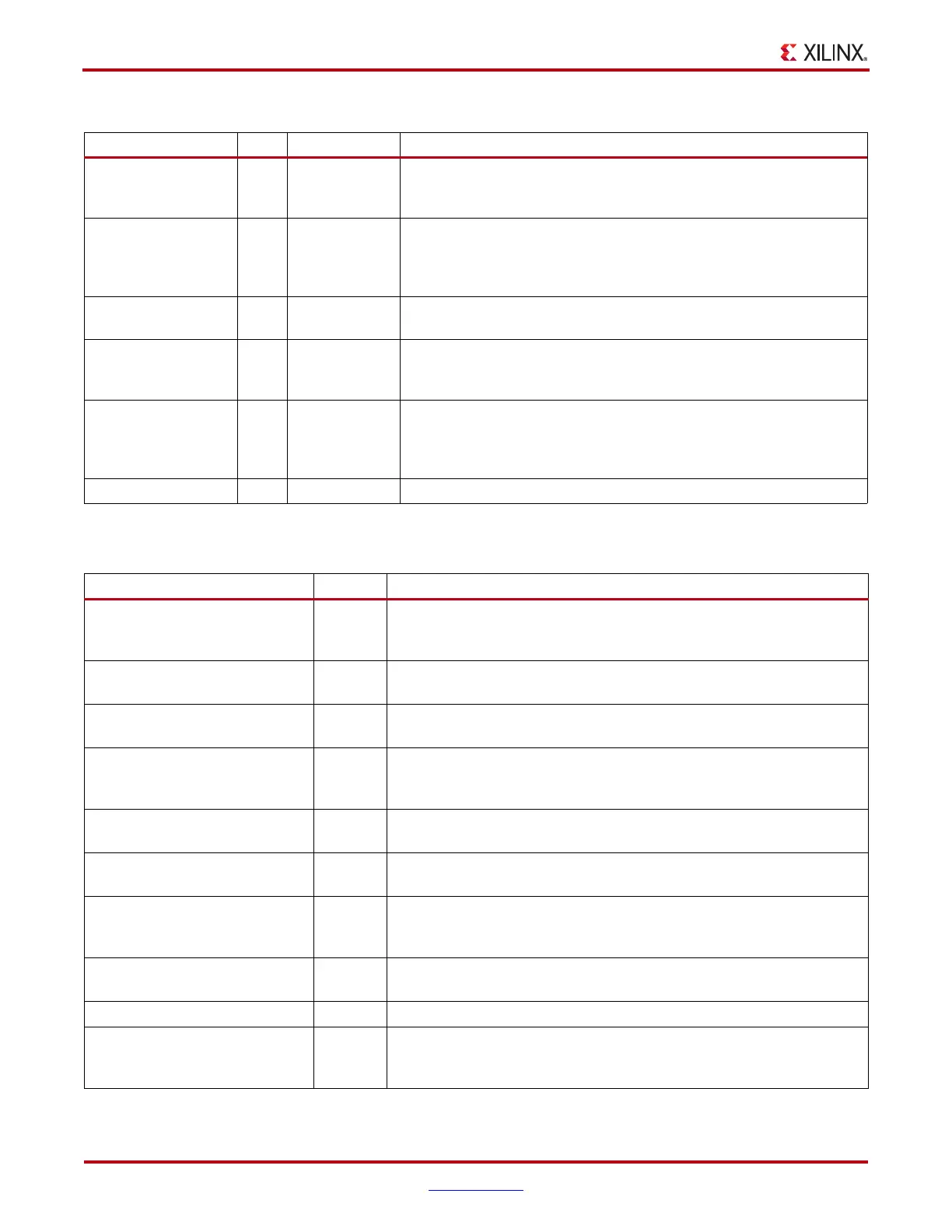

Table 4-53: RX Initialization Attributes

Attribute Type Description

CDR_PH_ADJ_TIME[4:0] 5-bit

Binary

Sets time to wait after deassertion of CDR phase reset before completion

of optional reset sequence for PCI Express operation during electrical

idle.

RX_EN_IDLE_HOLD_CDR Boolean Enables CDR to hold its data during optional reset sequence for PCI

Express operation during electrical idle.

RX_EN_IDLE_HOLD_DFE Boolean Enables the ability to restore DFE contents from internal registers after

termination of an electrical idle state for PCI Express operation.

RX_EN_IDLE_RESET_BUF Boolean Enables the reset of the receiver elastic buffer if a valid signal is not

present on the serial RX inputs. Works in conjunction with attributes

RX_IDLE_HI_CNT and RX_IDLE_LO_CNT.

RX_EN_IDLE_RESET_PH Boolean Enables the reset of the CDR phase circuits during optional reset

sequence for PCI Express operation during electrical idle.

RX_EN_IDLE_RESET_FR Boolean Enables the reset of the CDR frequency circuits during optional reset

sequence for PCI Express operation during electrical idle.

RX_EN_MODE_RESET_BUF Boolean Enables automatic reset of the RX elastic buffer when the

RXCHBONDMASTER, RXCHBONDSLAVE or RXCHBONDLEVEL[2:0]

ports change. See RX Channel Bonding, page 247.

RX_EN_RATE_RESET_BUF Boolean Enables automatic reset of the RX elastic buffer when the RXRATE[1:0]

ports change.

RX_EN_REALIGN_RESET_BUF Boolean Enables automatic reset of the RX elastic buffer during comma alignment.

RX_EN_REALIGN_RESET_BUF2 Boolean If this attribute is FALSE, the RX elastic buffer reset upon realignment

occurs only when the received signal from RXP/RXN is determined valid

and RXELECIDLE = 0.

Loading...

Loading...