148 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

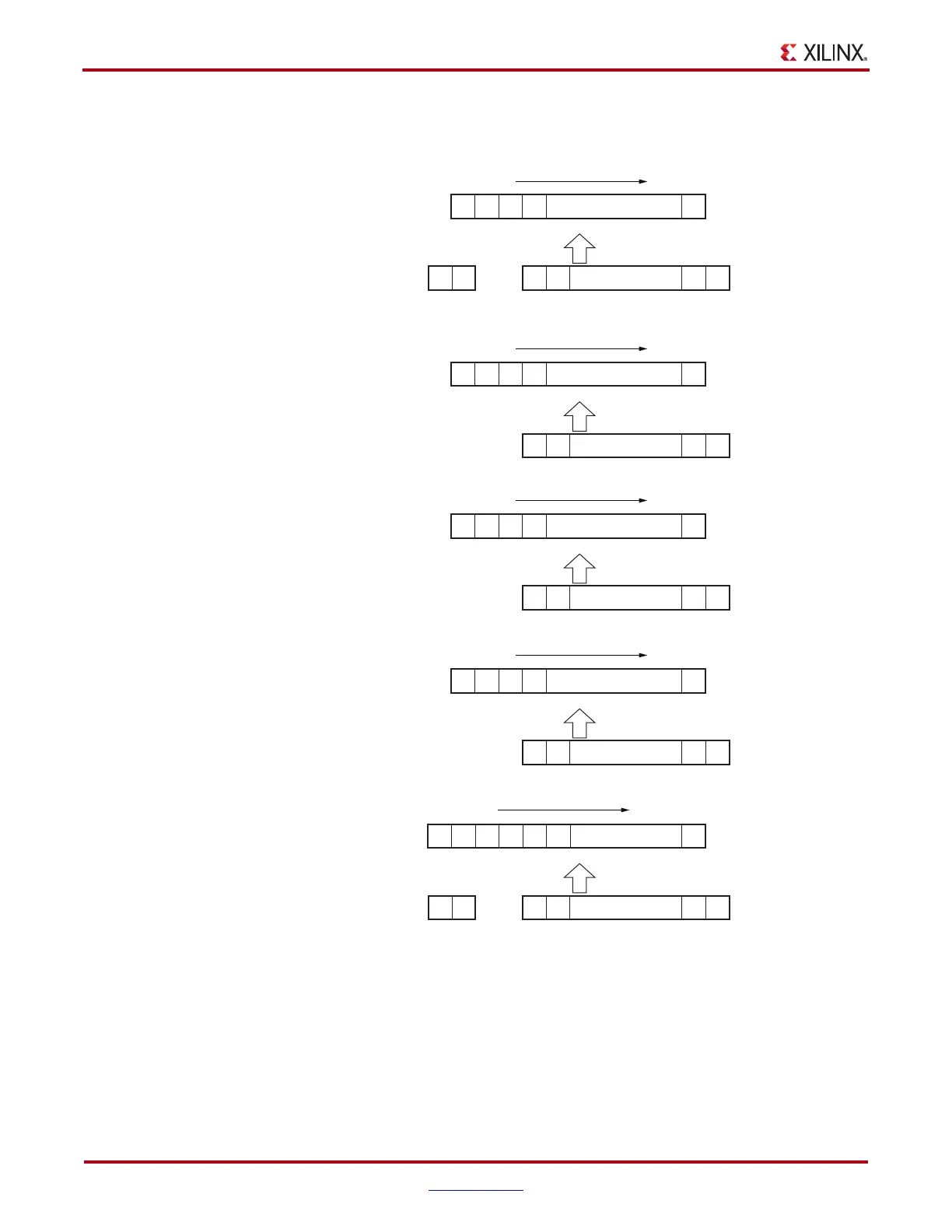

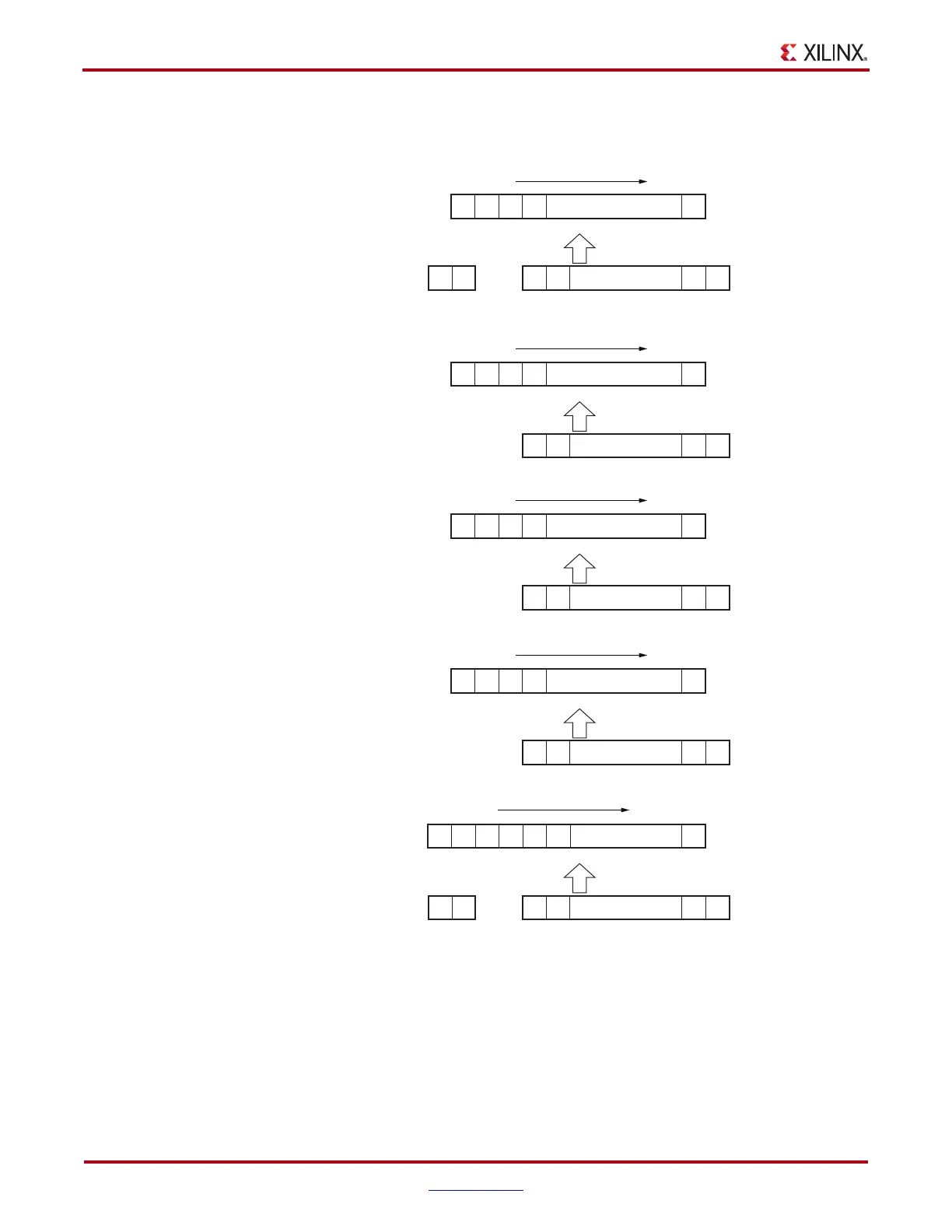

header of the second 66-bit block, and 12 data bits from the second 66-bit block. As shown

in Figure 3-13, the header bits are serialized first followed by the data bits.

TX Gearbox Operating Modes

The TX gearbox has two operating modes. The external sequence counter operating mode

must be implemented in user logic. The second mode uses an internal sequence counter.

The TX gearbox only supports 2-byte and 4-byte interfaces to the FPGA logic.

X-Ref Target - Figure 3-13

Figure 3-13: TX Gearbox Bit Ordering

UG366_c3_03_051509

Transmitted

First

Output of TX Gearbox

Cycle 0

TXDATATXHEADER

Transmitted

Last

H

...

...

1

H

0

D

15

D

14

D

15

D

14

D

2

D

1

D

0

H

1

H

0

Transmitted

First

Output of TX Gearbox

Cycle 4

TXDATATXHEADER

Transmitted

Last

D

...

...

1

D

0

H

1

H

0

D

15

D

14

D

4

D

1

D

0

H

1

H

0

Transmitted

First

Output of TX Gearbox

Cycle 1

TXDATA

Transmitted

Last

D

...

...

1

D

0

D

15

D

14

D

15

D

14

D

2

D

1

D

0

Transmitted

First

Output of TX Gearbox

Cycle 2

TXDATA

Transmitted

Last

D

...

...

1

D

0

D

15

D

14

D

15

D

14

D

2

D

1

D

0

Transmitted

First

Output of TX Gearbox

Cycle 3

TXDATA

Transmitted

Last

D

...

...

1

D

0

D

15

D

14

D

15

D

14

D

15

D

14

D

2

D

1

D

0

Loading...

Loading...