Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 205

UG366 (v2.5) January 17, 2011

RX CDR

The RX PLL provides a base clock to the phase interpolator. The phase interpolator in turn

produces fine, evenly spaced sampling phases to allow the CDR state machine to have fine

phase control. The CDR state machine can track incoming data stream that can have a

frequency offset, usually no more than ±1000 PPM, from the local PLL reference clock.

Methods for detecting CDR lock include:

• Finding known data in the incoming data stream (for example, commas or A1/A2

framing characters). In general, several consecutive known data patterns must be

received without error to indicate a CDR lock.

• Using the LOS state machine (see RX Loss-of-Sync State Machine, page 226). If

incoming data is 8B/10B encoded and the CDR is locked, the LOS state machine

moves to the SYNC_ACQUIRED state and stays there.

Ports and Attributes

Table 4-21 defines the RX CDR ports.

Table 4-22 defines the RX CDR attributes.

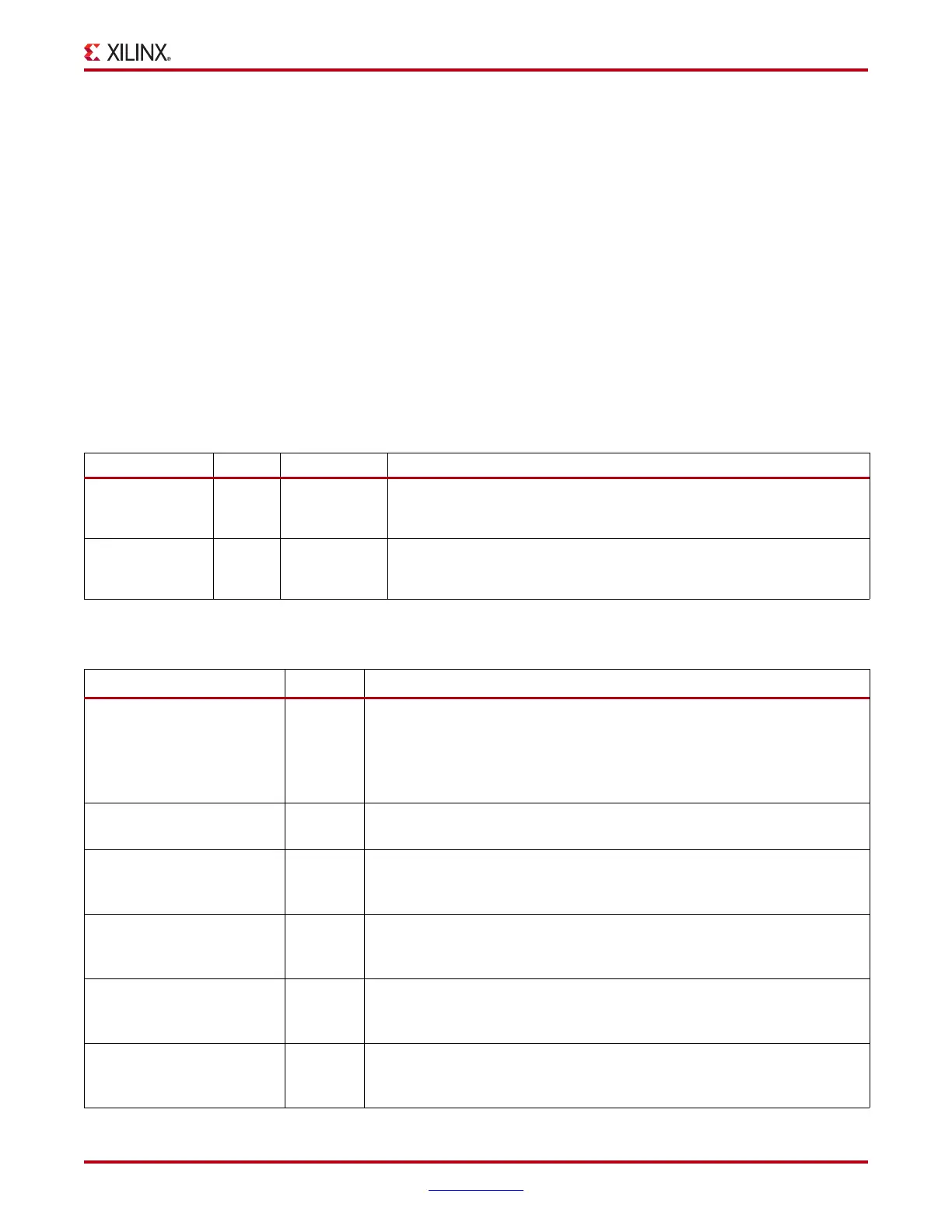

Table 4-21: RX CDR Ports

Port Dir Clock Domain Description

RXCDRRESET In Async Active-High CDR reset that resets the CDR logic and the RX part of the

PCS for this channel. This signal needs to be asserted whenever the

frequency of the RX PLL changes.

RXRATE[1:0] In RXUSRCLK2 This port and RX PLL output divider attribute, RXPLL_DIVSEL_OUT,

defines the line rate for the receiver based on the RX PLL frequency. Refer

to RX Fabric Clock Output Control, page 207 for more details.

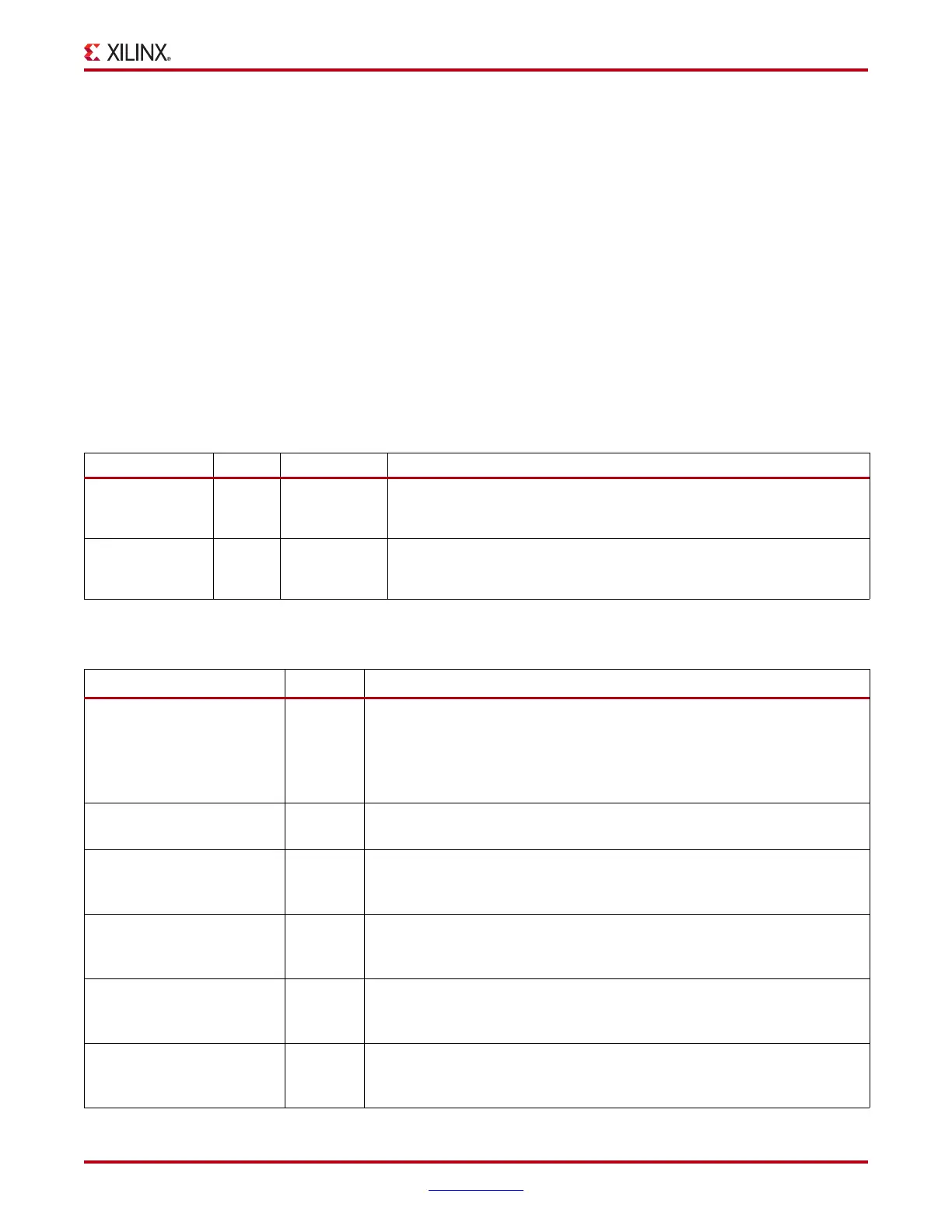

Table 4-22: RX CDR Attributes

Attribute Type Description

CDR_PH_ADJ_TIME 5-bit

Binary

Reserved. Use only recommended values from the Virtex-6 FPGA GTX

Transceiver Wizard.

This attribute defines the delay after deassertion of the CDR phase reset

before the optional reset sequence of PCI Express operation is complete

during electrical idle.

PMA_CDR_SCAN 27-bit

Hex

Reserved. Use only recommended values from the Virtex-6 FPGA GTX

Transceiver Wizard.

PMA_RX_CFG 25-bit

Hex

Reserved. Use only recommended values from the Virtex-6 FPGA GTX

Transceiver Wizard. For lock-to-reference operation, set PMA_RX_CFG to

25’h05CE000.

RX_EN_IDLE_HOLD_CDR Boolean When set to TRUE, it enables the CDR to hold its internal states during an

optional reset sequence of an electrical idle state as used in PCI Express

operation.

RX_EN_IDLE_RESET_FR Boolean When set to TRUE, it enables automatic reset of CDR frequency during an

optional reset sequence of an electrical idle state as used in PCI Express

operation.

RX_EN_IDLE_RESET_PH Boolean When set to TRUE, it enables automatic reset of CDR phase during an

optional reset sequence of an electrical idle state as used in PCI Express

operation.

Loading...

Loading...