Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 215

UG366 (v2.5) January 17, 2011

RX Pattern Checker

Ports and Attributes

Table 4-29 defines the RX oversampling ports.

Table 4-30 defines the RX oversampling attributes.

RX Pattern Checker

Functional Description

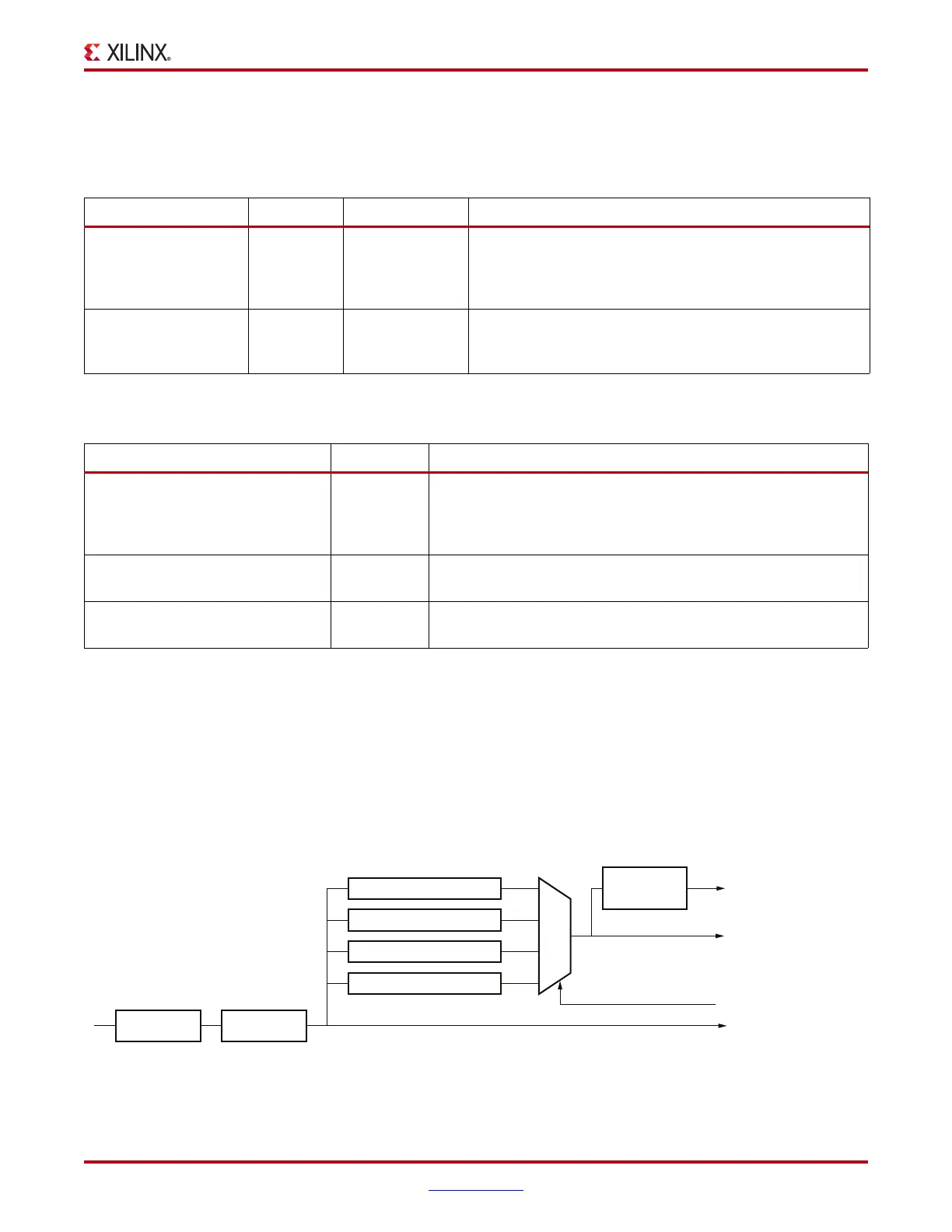

The GTX receiver includes a built-in PRBS checker. This checker can be set to check for one

of four industry-standard PRBS patterns. The checker is self-synchronizing and works on

the incoming data before comma alignment or decoding. This function can be used to test

the signal integrity of the channel.

Table 4-29: RX Oversampling Ports

Port Dir Clock Domain Description

RXENSAMPLEALIGN In RXUSRCLK2 When this port is High, the 5X oversampler in the PCS

continually adjusts its sample point. When this port is Low,

it samples only at the point that was active before the port

went Low.

RXOVERSAMPLEERR Out RXUSRCLK2 When this port is High, the FIFO in the oversampling circuit

has either overflowed or underflowed. The PCS must be

reset to resume proper operation.

Table 4-30: RX Oversampling Attributes

Attribute Type Description

PMA_RX_CFG 25-bit Hex This 25-bit attribute allows the operation of the CDR to be

adjusted. In normal operation, set the attribute PMA_RX_CFG to

the default value generated by the wizard. In oversampling mode,

PMA_RX_CFG is set to 25’h0F44000.

RX_OVERSAMPLE_MODE Boolean This attribute enables receiver oversampling when TRUE and

when 5X oversampling is On.

RXPLL_DIVSEL_OUT Integer RXPLL_DIVSEL_OUT must be set to 1 when using oversampling

mode.

X-Ref Target - Figure 4-20

Figure 4-20: RX Pattern Generator Block

RXDATA

RXENPRBSTST

Error

UG366_c4_18_120809

Polarity

Inversion

SIPO

PRBS-7 Pattern Checker

PRBS-15 Pattern Checker

PRBS-23 Pattern Checker

PRBS-31 Pattern Checker

Error Counter

(16 bits)

RX_PRBS_ERR_CNT

RXPRBSERR

Loading...

Loading...