138 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 3: Transmitter

Notes relevant to Figure 3-9:

• The minimum wait time from the rising edge of the TXPLLLKDET/RXPLLLKDET

signals to the first GTXTEST[1] reset pulse is 1,024 clock cycles.

• The minimum GTXTEST[1] pulse duration is 256 clock cycles.

• The minimum wait time between two GTXTEST[1] High pulses is 256 clock cycles.

If the transmitter uses TXPLL, the rising edge of TXPLLLKDET must be used to trigger

GTXTEST[1]. If the transmitter uses RXPLL, RXPLLLKDET must be used to trigger

GTXTEST[1].

Ports and Attributes

Table 3-7 defines the TX initialization ports.

Table 3-8 defines the TX initialization attributes.

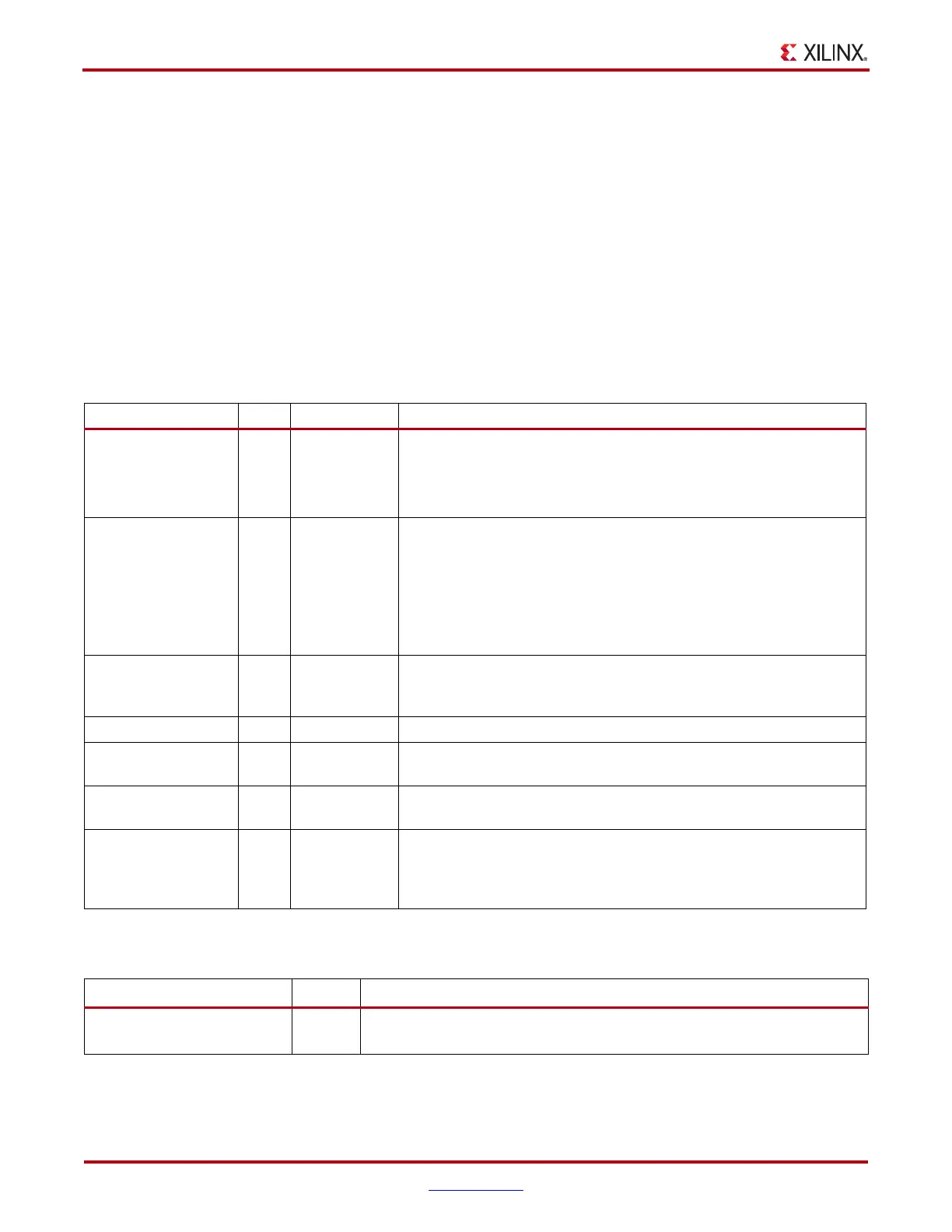

Table 3-7: TX Initialization Ports

Port Dir Clock Domain Description

GTXTEST[12:0] In Async GTXTEST[0]: Reserved. Tied to 0.

GTXTEST[1]: The default is 0. When this bit is set to 1, the TX output

clock dividers are reset.

GTXTEST[12:2]: Reserved. Tied to 10000000000.

GTXTXRESET In Async This port is driven High and then deasserted to start the full TX GTX

reset sequence. This sequence takes about 120 µs to complete and

systematically resets all subcomponents of the GTX TX.

If the RX PLL is supplying the clock for the TX datapath,

GTXTXRESET and GTXRXRESET must be tied together. In addition,

the transmitter reference clock must also be supplied (see Reference

Clock Selection, page 102).

PLLTXRESET In Async This port resets the TX PLL of the GTX transceiver when driven High.

It affects the clock generated from the TX PMA. When this reset is

asserted or deasserted, TXRESET must also be asserted or deasserted.

TSTIN[19:0] In Async Reserved. Must be tied to 11111111111111111111.

TXDLYALIGNRESET In Async This port resets the TX delay aligner for the TX buffer bypass mode.

See TX Buffer Bypass, page 155.

TXRESET In Async PCS TX system reset. Resets the TX FIFO, 8B/10B encoder and other

transmitter registers. This reset is a subset of GTXTXRESET.

TXRESETDONE Out Async This port goes High when the GTX TX has finished reset and is ready

for use. For this signal to work correctly, the TX reference clock and all

clock inputs on the individual GTX transceiver (TXUSRCLK,

TXUSRCLK2) must be driven.

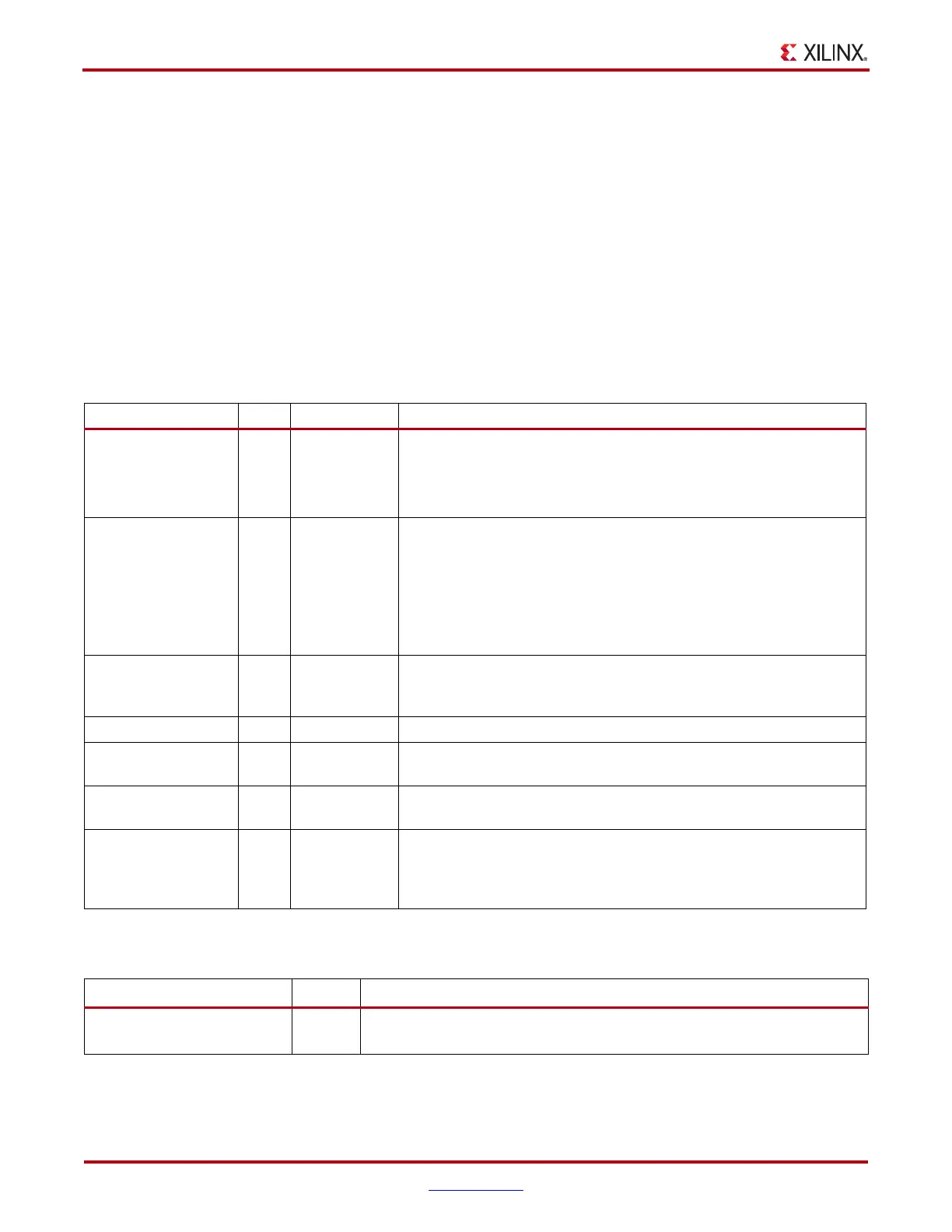

Table 3-8: TX Initialization Attributes

Attribute Type Description

TX_EN_RATE_RESET_BUF Boolean When set to TRUE, this attribute enables automatic TX buffer reset during a

rate change event initiated by a change in TXRATE[1:0].

Loading...

Loading...