Virtex-6 FPGA GTX Transceivers User Guide www.xilinx.com 137

UG366 (v2.5) January 17, 2011

TX Initialization

All reset ports described in this section initiate the internal transmitter state machines

when driven High. The internal reset state machines are held in the reset state until these

same reset ports are driven Low. The completion of these state machines is signaled

through the TXRESETDONE port.

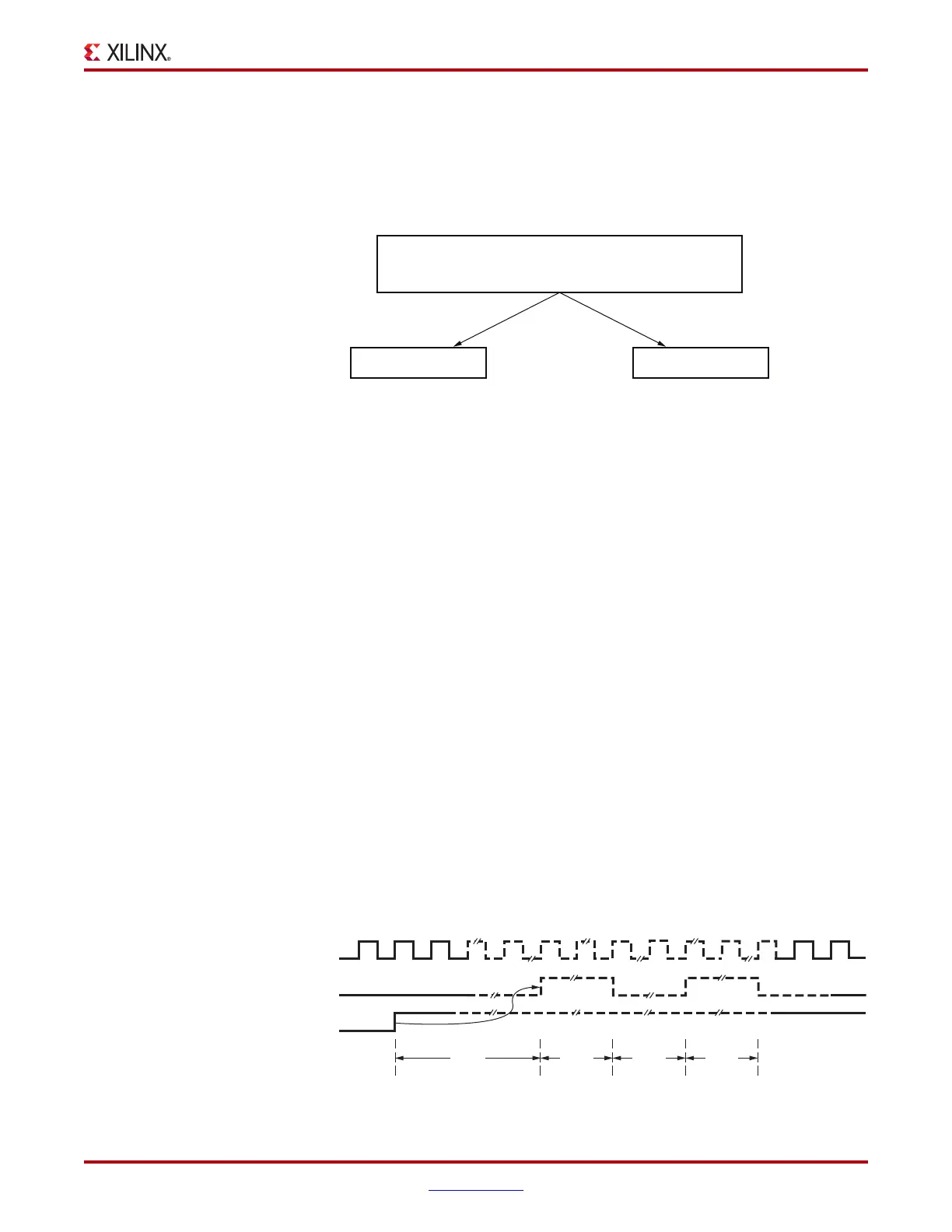

Figure 3-8 shows the GTX TX reset hierarchy.

When bypassing the TX buffer, GTXTXRESET, GTXRXRESET, PLLTXRESET, and

PLLRXRESET must not be tied High. Refer to TX Buffer Bypass, page 155 for more

information.

The GTX TX can use either TX PLL or RX PLL. Whichever PLL is used, if

TXPLL_DIVSEL_OUT is set to /2 or /4, the TX output clock divider must be reset twice

when the associated PLLLKDET signal goes from Low to High. Resetting the TX output

clock divider twice (double reset) is achieved through the GTXTEST[1] port, and is

required under these conditions:

• When the TX output clock divider, TXPLL_DIVSEL_OUT, is set to /2 or /4

• After FPGA power-up and configuration

• After the associated reset of the PLL used by the TX is toggled

• After turning on a reference clock to the PLL used by the TX

• After changing the reference clock to the PLL used by the TX

• After assertion/deassertion of TXPOWERDOWN

• After assertion/deassertion of GTXTXRESET

The circuit that implements the double reset through GTXTEST[1] must use a free running

clock. This clock can be sourced from:

• IBUFDS output. This also provides the MGTREFCLK to the GTX transceiver.

•DRP clock.

• Any other free running clock from the user design.

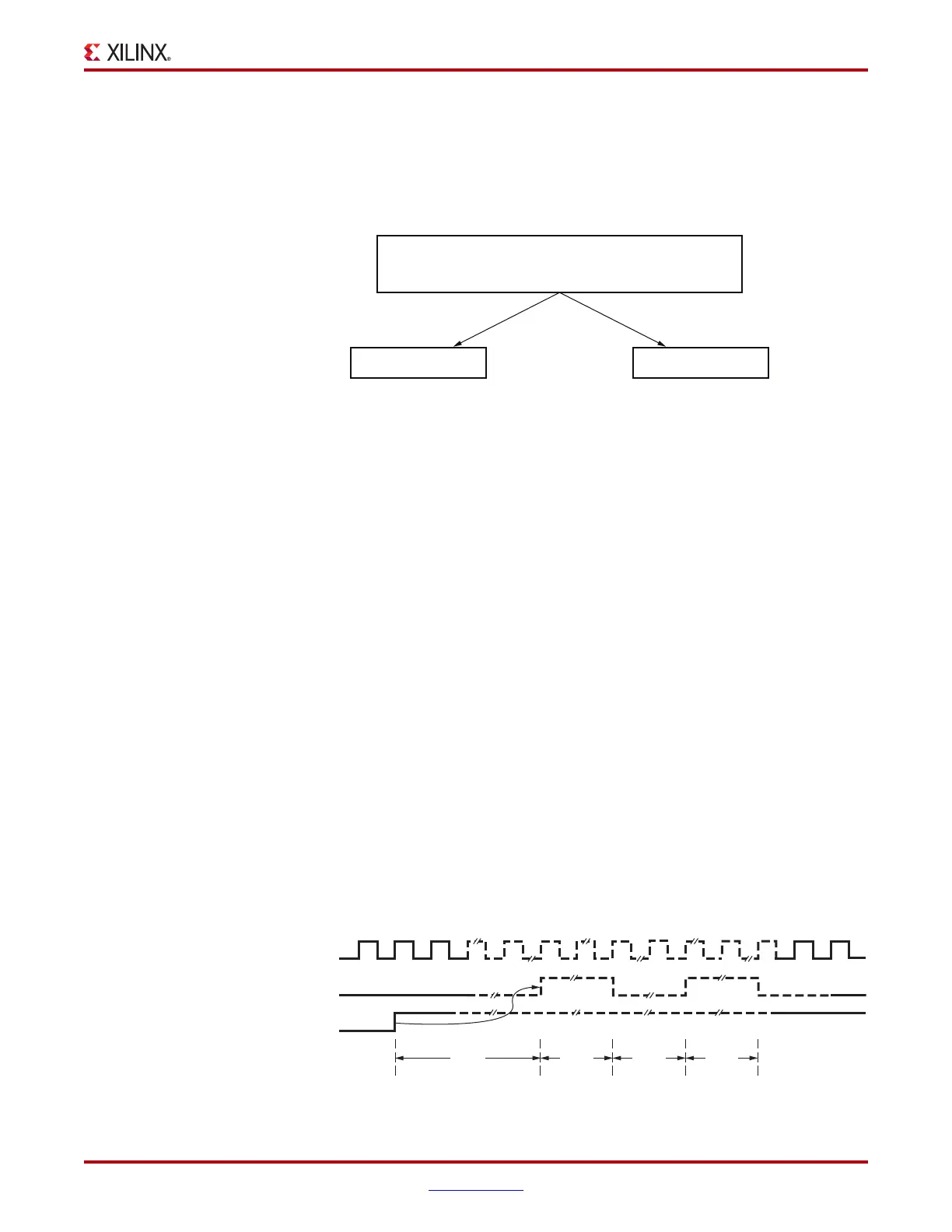

The circuit must follow the timing diagram shown in Figure 3-9.

X-Ref Target - Figure 3-8

Figure 3-8: GTX TX Reset Hierarchy

X-Ref Target - Figure 3-9

Figure 3-9: Transmitter Reset After Configuration

After Configuration or GTXTXRESET or

Falling TXPLLPOWERDOWN

PLLTXRESET TXRESET

UG366_c3_27_061109

CLK

GTXTEST[1]

TXPLLLKDET /

RXPLLLKDET

UG366_c3_33_092410

1024

CLKs

256

CLKs

256

CLKs

256

CLKs

Loading...

Loading...