256 www.xilinx.com Virtex-6 FPGA GTX Transceivers User Guide

UG366 (v2.5) January 17, 2011

Chapter 4: Receiver

RX Gearbox

Functional Description

The RX gearbox uses output pins RXDATA[31:0] and RXHEADER[2:0] for receiving data.

Similar to TX Gearbox, page 146, the RX gearbox operates with the PMA using a single

clock. Because of this, occasionally, the output data is invalid. Output pins

RXHEADERVALID and RXDATAVALID determine if the appropriate header and data are

valid. The RX gearbox only supports 2-byte and 4-byte interfaces. A 1-byte interface is not

supported.

The data out of the RX gearbox is not necessarily aligned. Alignment is done in the FPGA

logic. The RXGEARBOXSLIP port can be used to slip the data from the gearbox cycle-by-

cycle until the correct alignment is reached. It takes a specified amount of cycles before the

bitslip operation is processed and the output data is stable.

Descrambling of the data and block synchronization is done in the FPGA logic.

Ports and Attributes

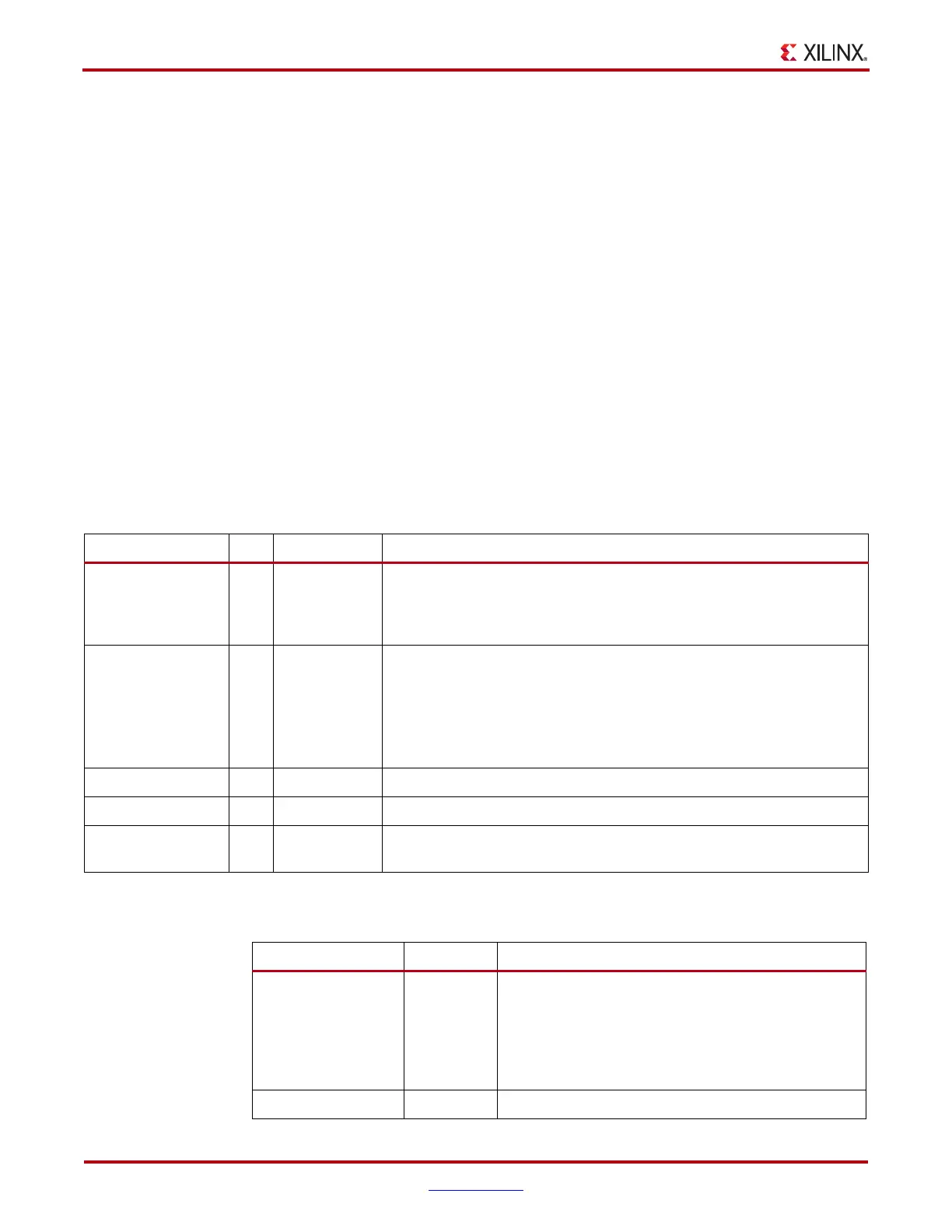

Table 4-50 defines the RX gearbox ports.

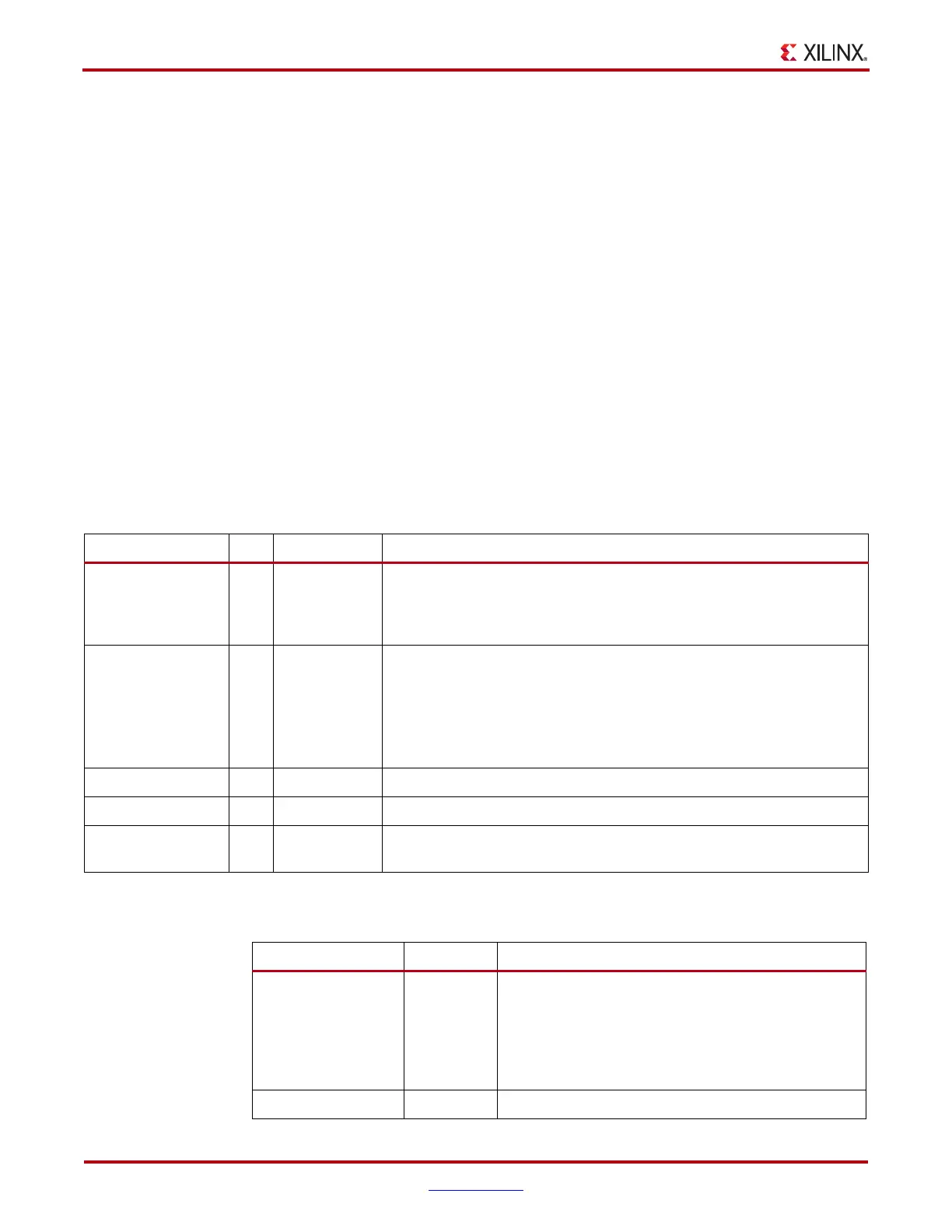

Table 4-51 defines the RX gearbox attributes.

Table 4-50: RX Gearbox Ports

Port Dir Clock Domain Description

RXDATAVALID Out RXUSRCLK2 Status output when Gearbox 64/66 or 64/67 is used, which indicates that

the data appearing on RXDATA is valid. For example, during 64B/66B

encoding, this signal is deasserted every 32 cycles for the 4-byte interface

and every 64 cycles for the 2-byte interface.

RXGEARBOXSLIP In RXUSRCLK2 When High, this port causes the gearbox contents to slip by one bit. It is

used to achieve alignment with the FPGA logic. Asserting this port for

one RXUSRCLK2 cycle changes the data alignment coming out of the

gearbox.

When RXGEARBOXSLIP is asserted for more than one cycle, the gearbox

realigns the data once for each RXUSRCLK2 cycle that it is held High.

RXHEADER[2:0] Out RXUSRCLK2 Header outputs for 64/66 (1:0) and 64/67 (2:0).

RXHEADERVALID Out RXUSRCLK2 Indicates that the RXHEADER is valid when using the gearbox.

RXSTARTOFSEQ Out RXUSRCLK2 When Gearbox 64/66 or 64/67 is enabled, this output indicates when the

sequence counter is 0 for the present RXDATA outputs.

Table 4-51: RX Gearbox Attributes

Attribute Type Description

GEARBOX_ENDEC 3-bit Binary Gearbox Modes:

000: 64B/67B using external sequence counter

001: 64B/66B using external sequence counter

010: 64B/67B using internal sequence counter

011: 64B/66B using internal sequence counter

RXGEARBOX_USE Boolean When TRUE, this attribute enables the RX gearbox.

Loading...

Loading...